Design与FAB的桥梁2-《Design Rule》 (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

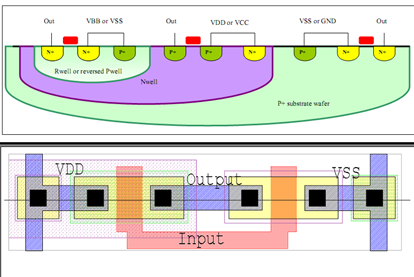

上一章讲完了SPICE Model,它是Design与FAB的第一道桥梁,如果它用我们的Model做电路仿真能够得出他需要的输入输出特性,则表示我们制程和电性参数是符合他们要求的。那接下来他们需要通过第二道桥梁“Design Rule-设计规则”来将他的电路转换成Layout/版图,然后通过tape-out做成光罩,我们FAB拿到光罩就可以帮设计公司跑出Wafer了。

我们今天学习的主题就是Design Rule (设计规则)。

1、何为设计规则?

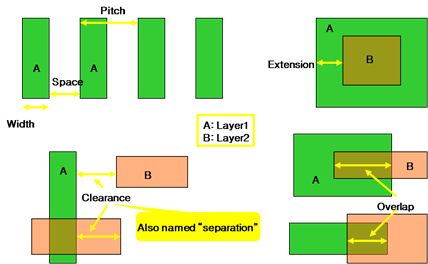

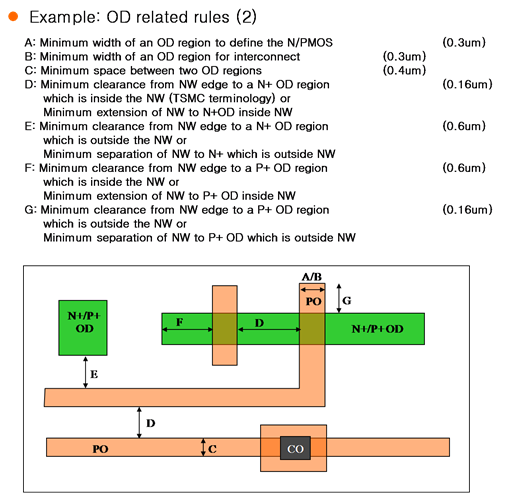

说白点就是画版图需要遵循的规则,每一层的尺寸和间距(也就是Line和Space:Line+Space=Pitch)需要画多少?当然这个尺寸是FAB根据我们的制程能力(主要是黄光)来制定的,因为Line和Space是用来定义当层的尺寸规则,所以它只是考虑黄光机台的resolution,而图形除了当层特性外,还需要考虑的就是前后层的套刻对准问题,所以有三个rule:Extention、Clearance、Overlap。而Extention主要指后面一次把前一层图形包裹起来,并四面凸出去的尺寸,主要考虑黄光的对准能力的variation。而Clearance是指两层图形之间的距离,除了考虑对准能力还要考虑制程隔离特性,而Overlap主要指两层图形交叠的部分。

不言而喻,我们的制程如果想要有优势就必须在这些尺寸上做的比别人小,这样我们提供的芯片尺寸才能比别人小,所以说设计规则是FAB制程能力的重要指标。当然我们的目标不是为了小,而是在小的情况下还要能够有好的performance和高的Yield,所以我们的rule还需要够完整并且尽可能面面俱到比如ESD,mismatch,layout balance,dummy pattern以及Stress等等。

2、设计规则的由来!

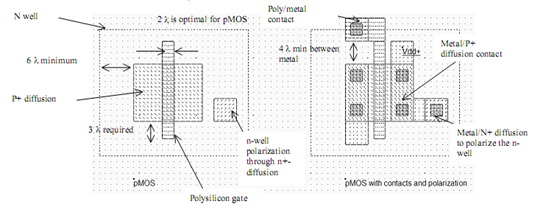

设计规则最早制定是有MOSIS提出来的λ rule,它定义最小尺寸(Gate)的一半为一个λ,其他所有尺寸都是λ的倍数来定义,便于等比例缩小(Scanable)早期在摩尔定律以及SIA road map下走的很好。

后来摩尔定律走到亚微米的时候,很多小尺寸下的寄生特性不一样,所以每个尺寸不能单纯的用Lambda的倍数来表达了,所以需要单独对每个尺寸进行window check来确定real的尺寸需要定义为多少,我们称之为Design rule的DRC,其实就是尺寸对电性的sensitivity,我们姑且称之为微米规则(um rule),不是说你可以随便定义哦,而是不再呆板的用Lambda的倍数了。好处是它可以更合理化,不好的地方是所有尺寸都要Verify过。

而对于现代化的FAB来说,一般在RD阶段,他们会先用TCAD做simulation,从理论上预计出每一层需要的尺寸是多少,得出V0版的设计规则。然后根据V0版规则画好Test key/vehicle,并且针对每个尺寸画不同尺寸的test key去跑real的Silicon data去验证这些不同尺寸下的数据,收集sensitivity去check window,并最终finalize V1.0版设计规则提供给客户,在设计规则初期你可以根据客户的feedback修正你的规则,但是大量量产之后尽量不要修改你的规则,因为修改你需要通知已经用过的客户,而且表示你有问题,那很多以前的客户或产品会question你之前没修改过的产品有没有risk,除非你能说服客户,否则你可能面临call-back。(当然你也可以不用修改设计规则而达到目的~~)

3、设计规则需要考虑哪些因素?

通常客户看到的都是real的on silicon的尺寸,可是实际上我们做FAB的人都知道,蚀刻有etch bias,黄光曝光到wafer也会有差,所以我们需要在做光罩的时候把这个process bias加进去,这样才能保证Final是客户想要的尺寸。

举个例子,0.35um的OD是0.5um,所以客户画好了0.5um,而鸟嘴每边占掉了0.1um,所以如果我们按照客户实际画的去做,那客户final得到的就是0.48um,那他要跟你闹了。。。。所以我们在做光罩的时候会提前加0.1um/side的Logic operation,这样on mask实际就是0.5um微米,然后on silicon才是0.5um。

通常design rule的migration是指特征尺寸,也就是Gate CD,它是最关键决定MOSFET的特性的。基于SIA roadmap我们会定义为1.0um->0.7um->0.5um->0.35um->0.25um->0.18um->0.13um->0.11um,几乎每个时代都是shrink 70%来的(因为摩尔定律规定面积需要shrink一半)。当然大家也能看到过渡时代,比如0.16um, 0.152um等等,主要是由于很难从0.18um直接过渡到0.13um因为制程技术有很多难点需要客服,所以需要慢慢shrink。

当然,FAB规定的设计规则可以cover大部分情况,但绝对不是完美的,很多有经验的设计工程师会考虑宏观因素,比如电路模块的摆放与信号走向一致,主信号线路尽量短少拐弯且长度相等,不同模块电源和接地要分开且防止干扰,尽可能把电容电阻和大晶体管放在chip边缘提高抗干扰能力等等。这些都是know-how了!当然更有牛X的设计者艺高人胆大自己去偷rule,当然出了问题自己就摸摸鼻子理亏,不过他还是会跟你Argue,谁让他是你的上帝呢?所以做为FAB你需要有一个强大的DRC在他tape-out的时候就要把他拦下来。

支付宝打赏

支付宝打赏  微信打赏

微信打赏