如何巧用C-V曲线来查Case(转)

随着半导体制程越来越复杂,我们最关键的参数Vt的控制越来越重要,有的时候我们的Vt如果单纯是衬底浓度影响我们自然可以通过长沟和短沟以及NMOS和PMOS是否同时变动来确定是否是GOX还是Vt_IMP的问题,其实这也是一种correlation它其实是一种逻辑思考方式,只是他是基于理论的。不像现在很多年轻的工程师直接从wafer start直接丢到系统里run到WAT,也能找到问题,可是那不是工程师干的活。

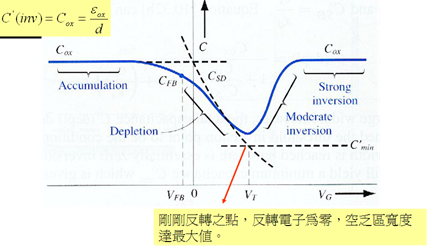

今天我们就来讨论下MOS的C-V曲线与衬底浓度以及GOX特性的关系,这样大家既可以用它来评估GOX特性,也可以用C-V曲线来判定Vt 的Case是由于什么造成的,其实同时也是为了介绍这个MOS晶体管的栅极结构的C-V特性,既有助于我们理解这个理论,又可以用实际案例来验证。

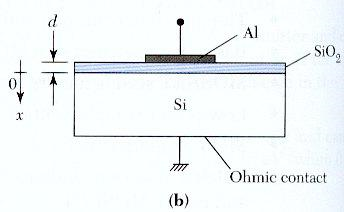

讲到MOS电容,他的结构就是Gate-Oxide-Semiconductor的夹心电容结构,其实就是高中物理讲的平板电容结构。而我们实际的平板电容的C-V特性下的电容式恒定值,因为电容公式高速我们电容只和介电常数以及厚度和面积相关,所以和电压无关。不过MOS结构的电容会随着电压的变化而变化,这里且听且分析吧~

MOS-Cap的电容结构很简单,忽略源漏极就只剩下Gate-Oxide-Semiconductor(Well)了。所以叫MOS,也叫MIS(Metal-Insulator-Semiconductor),现在到65nm以下的制程因为要用的Hi-K的栅极介质层,所以更倾向用MIS而不用MOS了。

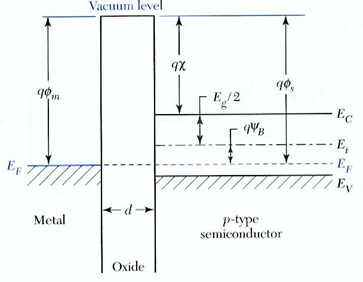

在我们介绍这样的MOS-C的结构之前,先介绍一个概念平带电压(Vfb, Flat-Band Voltage)。当栅极无偏压时候,理想情况下金属功函数qΦm与半导体功函数qΦs的能量差应该为零,也就是金属和半导体的功函数差qΦms等于零。也就是说零偏压下,能带是平的所以叫做平带。而在栅极接正电压或负电压,则半导体一边的能带会受到下拉或上移影响而弯曲。