栅极介质层的质量评估 (GOI) (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

随着MOSFET的尺寸越来越小,栅极介质层的厚度也是越来越薄。作为MOSFET的核心,Gate OXide的可靠性一直都是最主要的制约器件是否可以量产的因素之一。前面我们几乎讲完了Gate Electrode和Gate Dielectric两个部分,今天我们该趁热打铁把Gate Dielectric的可靠性讲完,其实就是我们FAB里面经常讲的GOI测试。

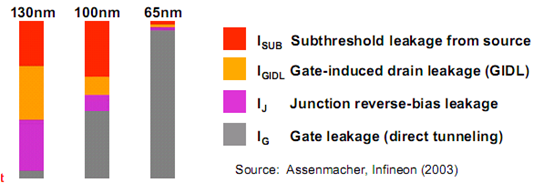

随着GOX的一直无限制的减薄,我们面临的问题是栅极漏电直接变得不可忽略,甚至直接导致Gate进入热击穿而烧毁,所以评估栅极抗压能力将是这个器件寿命的重要指标。

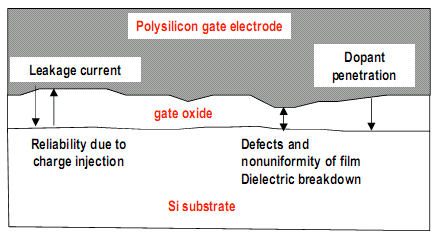

在评估Gate Dielectric的效能之前,我们先讨论下通常Gate Dielectric都是怎么失效的,然后根据它的失效机理再去想怎么评估会比较能理解和记忆。

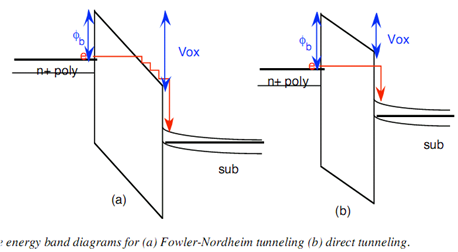

如上所述,我们GOX一直在down薄,到了0.13um甚至<20A了,当厚度减小带来的直接问题就是Gate对衬底的电场显著提高了,那这个栅极介质层也不会持续 保持他的绝缘性了,会发生Quantum Mechanical Tunneling导致直接漏电。通常这种Tunneling有两种方式,F-N tunneling和Direct tunneling (上一篇文章<Gate Dielectric>已经讲过了)。

上面都是讲的减薄会带来的direct tunneling问题,这种只能靠提高介质常数来等效换取厚度了,类似的理论在我们Low-End process里面也有比如用ONO Capacitor代替HTO Capacitor换取高BV的电容。那F-N Tunneling呢?它是一个类似Trap Assisted (陷阱辅助)的隧穿,字面理解就知道它一定的借助于Trap,而这个trap从哪里来?它就是栅极氧化层被损伤了或者没长好带来的缺陷陷阱中心,我们称之为栅极氧化层损伤(damage),下面介绍下GOX损伤的几种机理。

查看隐藏内容

支付宝打赏

支付宝打赏  微信打赏

微信打赏