半导体厂商如何做芯片的出厂测试?

所有的测试项都是在ATE上执行的,一般会执行几秒到几十秒,因为ATE是根据机时来付费的(很少有海思,苹果这种土豪公司一次买数十台),所以缩短测试时间变得尤其重要!另外一般芯片在量产测试的时候,都是百万颗或者千万颗,每个芯片节省一秒,总体来说缩短的时间还是很可观的。

在测试执行完成后,ATE会输出一个Datalog,以显示测试结果。对于测试pass或fail测试项的不同,也会对其进行分类(Bin),最后由Handler分拣。

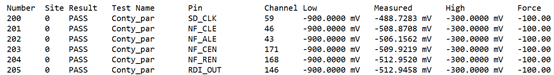

datalog 示意图:

以上就是芯片的测试完整流程。再放两张芯片测试的封测厂/实验室的环境图:

至于题主的两个问题:

1、BGA 这样的封装,应该不能多次焊接吧,那又如何上电测试呢?

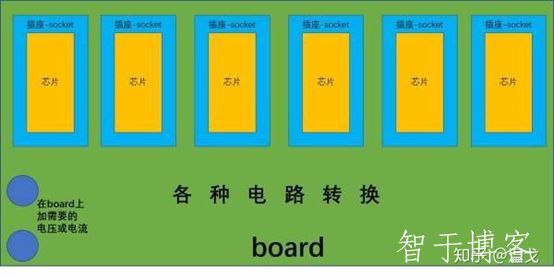

对于封装好的芯片,通常测试是不需要进行焊接的,它和ATE机台的连接方式是通过socckt和Load board。

socckt也就是放芯片的底座,长这样:

不同大小,不同封装类型的芯片,socckt也不同,有专门的做这个的厂商。

先把芯片放到socckt里,再把socckt放到load board上,load board再放在机台上。有的load board很重,对很多女同志来说搬起来是有些辛苦啊!

一个load board上面支持放多个socckt,我们称其为site。示意图如下,共6个site,可以对6个芯片同时进行测试:

2、那么多的功能,真的要写软件一样一样测吗?很费时间吧

在这里先说明一下,芯片的逻辑功能是有IC验证工程师来完成的,是在流片之前,并不依赖于测试。

而芯片测试里的function test/structure test是跑pattern, 测试的是在制造过程中芯片是否有缺陷,从而影响功能/性能。

所以测试工程师所需要的关心的就是把pattern都跑通,如果跑不通可能会和DFT工程师一起进行diagnosis。

测试工程在写测试项的时候,也不是要一行一行代码去写,通常ATE机台的嵌入式软件都有提供测试项的Template, 只需要填写参数就好。另外针对一些大客户的成熟测试项,也会开发一些测试模板,留好必要的参数接口,这样就很方便应用到其他的芯片测试上。

写在最后:

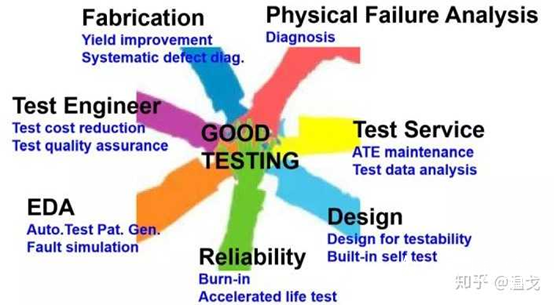

一个完备的的芯片测试不是靠芯片测试工程师一个人完成的,而是需要设计工程师,DFT工程师的支持,以及由可靠的EDA工具,优秀的硬件支撑等多方因素共同决定的。

芯片测试是极其重要的一环,有缺陷的芯片能发现的越早越好。在芯片领域有个十倍定律,从设计-->制造-->封装测试-->系统级应用,每晚发现一个环节,芯片公司付出的成本将增加十倍!!!

所以测试是设计公司尤其注重的,如果把有功能缺陷的芯片卖给客户,损失是极其惨重的,不仅是经济上的赔偿,还有损信誉。因此芯片测试的成本也越来越高!

在 IC 行业,每一个环节都要十分小心,一次流片的费用在数十万美金,一天的ATE机台使用几百美金。而一个芯片的利润可能只有几美分。这也是IC行业投资周期长,收益少的原因,基本前几年都在亏钱。幸运的是国家越来越重视芯片了,期待国内IC发展能越来越好。

以上,共勉!