晶圆制备–外延(Epitaxy) (转)

上一篇文章专题介绍晶圆制备,如何制备集成电路制造专用的衬底晶圆片?我们一般6/8寸的logic、MS制程用的都是抛光片(polish wafer),这种圆片都是在坩埚里面单晶直拉法拉的晶棒(ingot),然后切割(saw)成一片片的wafer,再经过抛光退火形成最终的Wafer卖给FAB。

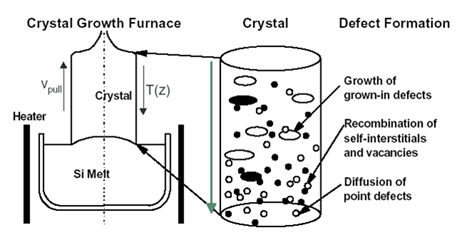

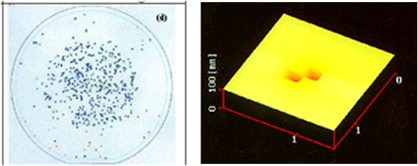

但是这种CZ法(单晶直拉法)做出来的wafer最大的问题就是因为坩埚会带入含碳或含氧的杂质,而这些杂质会在晶格生长过程中产生缺陷,我们称之为原生缺陷或者叫生长缺陷(grown-in defect),而这种缺陷经过APM清洗(SC1: NH4OH: H2O2: H2O=1:1:5)之后会产生很多缺陷,而最初人们不知道是什么于是定义为颗粒(Particle),但是后来发现这种颗粒随着APM清洗非但没有减少反而大小和数量都增加了,后来的研究发现这是晶格生长过程中的晶格原生缺陷(COP: Crystal Originated Particle),而且以前的GOI fail几乎就是这种原因。(后面再讲COP缺陷的形成机理吧~~不然就偏题了)

如何消除这种晶格生长过程中的原生缺陷?除了前面讲抛光片里面的退火处理外,最完美的解决方案就是外延了(台湾语叫磊晶, Epitaxy,简称EPI)。外延这个词来源于希腊语【"Epi"上面】以及【“taxis”整理安排】的组合"Epitaxy"。

就是在抛光片上面再长一层高质量的单晶硅,因为没有了坩埚(主要含氧和碳),所以就没有坩埚引入的杂质诱生的原生缺陷。而外延的缺陷是由衬底决定的,它会沿着衬底径向继续沿径向结构累加原子。我们通常的外延衬底片都是polish wafer也是硅,这种外延与衬底是同种材料的称之为同质外延(Homoepitaxy),也就是我们广义上简称的外延。如果外延与衬底材料不一样,则为异质外延(Heteroepitaxy),比如SOS(Silicon on Sapphire, 蓝宝石)衬底。

外延主要应用于双极性(BJT)、BiCMOS、或者高要求/低漏电的CMOS、或者高压CMOS制程里,通常厚度在3~7um。减少了CMOS电路的栅锁效应(Latch-up),提高BJT的放大系数以及高压器件的耐压等作用。当然外延也有缺点,比如工艺复杂价格昂贵(翻倍),安全问题(SiH4和H2都是易燃易爆的),扩散和自掺杂效应,图形冲坏(shift)。

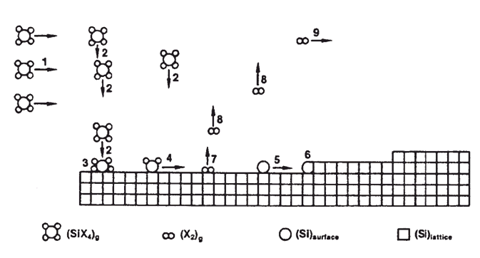

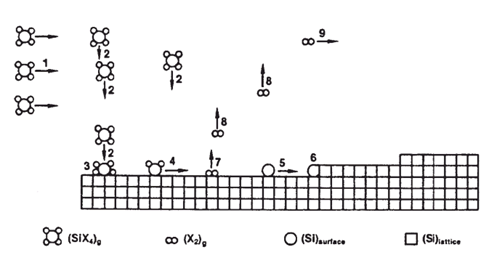

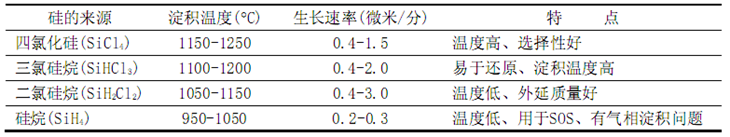

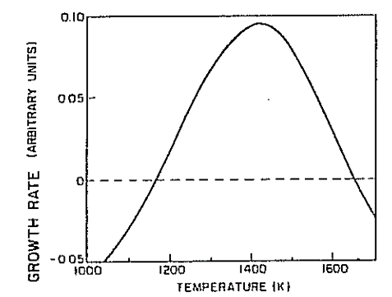

外延是个化学气相沉积(CVD)过程,主要用硅的气态化合物(SiCl4, SiHCl3, SiH2Cl2, SiH4)与H2发生还原反应生成硅(Si),一般包含五个步骤:1) 反应物被运输到衬底上,2)反应物被吸附到衬底上,3) 表面发生化学反应生成薄膜和副产物,4) 反应物从表面被放出,5) 副产物从表面被运走。主要是前三个步骤,气流流过与衬底形成滞留层,其厚度与气流速度以及表面形貌有关,气流越快则滞留层越薄。而反应气体需要闯过滞留层才能到达Si表面发生发生反应,而且副产物需要及时被带走,否则副产物的HCl又反过来蚀刻Si (可逆反应,可以利用此原理来做vapor clean)。所以说反应速率正比于气体中的摩尔分数,低温时反应物进入表面但是反应太慢,所以对温度敏感性不强。高温时,由于反应比较激烈,所以质量输运(Mass Transportation)占主导。而质量输运的主要因素就是滞留层宽度,而滞留层宽度与气体流速有关,所以反应腔室的设计如何保证均匀的层流(laminar)是很重要的,否则发生湍流(turbulent)就有厚度均匀性问题了。

外延反应主要气体是SiCl4、SiHCl3、SiH2Cl2、SiH4。最常用的是SiCl4与H2发生还原反应。

但是他们有中间产物HCl和SiCl2,而且是可逆的,且可以蚀刻Si,实验证明在低温(<900C)和高温(>1400C)的时候都是会发生蚀刻反应的,所以速率会降低(负生长)。也有用硅烷(SiH4)直接分解反应,这种反应没有HCl,所以不会有可逆反应,而且不需要高温就可以反应,但是它主要的缺点也是因为没有HCl,因为Cl可以带走Fe、Cu类金属杂质,因为是分解反应,所以很容在容器壁产生沉积颗粒。

外延的固态扩散和自掺杂效应:

外扩散/固态扩散(Solid-state Diffusion or Outdiffusion):指高温下杂质原子会扩散进入到已经生长的外延层中,导致外延层阻值发生变化。

自掺杂(Autodoping):衬底的掺杂原子在高温下扩散进入气体中被滞留层俘获又重新在反应气体中进入到外延层。

外扩散和自掺杂效应都会增加衬底到外延的过渡层,在接近衬底处,外扩散为主要因素,形成一个较宽的过渡层,可以通过快的生长速率,或者用低浓度衬底、或者用锑(Sb, antimany)注入形成埋层等来降低这一问题。自掺杂效应可以通过衬底封住一层film来降低(比如oxide seal)。

外延的缺陷:

外延前必须对衬底做处理,否则长的晶向肯定错乱了,所以B-clean是必须的。但是这样还是不够的,还需要一个1100C高温下的HCl (1~5%HCl的H2)去in-situ蚀刻吃掉表面的硅。为什么用1~5%HCl呢?因为高温下这个反应很快,很容易吧硅干掉。所以后来也有少数1050C的SF6 in-situ Vapor Clean替代的,但是还是用HCl比较好,因为Chamber里面的parts是含金属的,虽然有SiC coating的,但是毕竟还是有金属渗出来,还是用含Cl的气体Clean比较好。

主要的外延缺陷有位错(Dislocation)和层错(stacking faults),位错主要来自衬底的位错线延伸到外延中,所以对衬底的选择很重要。而层错主要来自衬底和外延的晶格不匹配(如掺杂差异)而失配位错(misfit dislocation),还有一种层错来源是由于热应力超过了硅的屈服应力(yield stress,指形变极限)造成了滑移线(Slip line),一般可能是正面和背面温度差造成的,所以对EPI wafer的形变要求很高。一般情况下,堆垛层错(stacking faults)主要来自于衬底表面的微小台阶或者衬底或腔体的杂质,这些都会对沿晶向生长受到障碍导致堆垛次序错误,在随后的氧化过程中会诱生出氧化堆垛层错(OISF: Oxide Induced Stacking Faults)。

如何减少外延缺陷?

1) 衬底要干净、无缺陷;

2) Chamber要干净,热辐射要均匀;

3) 衬底少台阶,减少衬底与外延的浓度差

4) recipe要优化,如气流要均匀,升降温要控制;

5) 增加应力层:我不懂,貌似是SiGe技术吧。

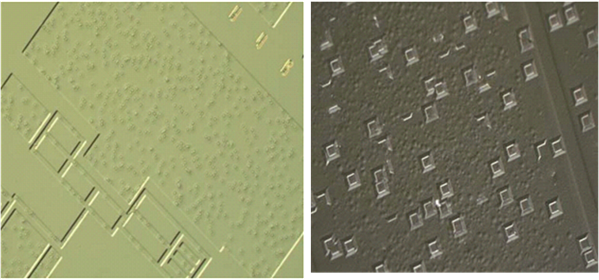

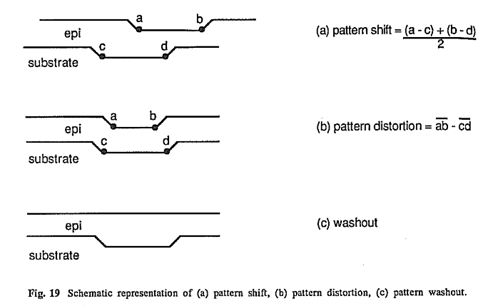

外延的图形漂移:

外延的另外一个重要特性就是会发生台阶图形漂移(Pattern shift, pattern distortion),所以必须要在后续的光罩中做补偿。但是这个漂移量是很复杂的,取决于晶向、沉积速率、温度、以及衬底等。据说<100>晶向上是刚好晶向上shift最小,<111>晶向是在偏离晶向2~5deg方向上shift最小,所以<111>衬底的外延必须用偏离3度角的衬底片。温度和沉积速率的影响是:温度增加移动减少,沉积速率增加移动增加,减压的沉积能大大减小移动,使用SiH4的分解沉积能消除pattern shift (主要是因为Cl2/HCl的影响)。

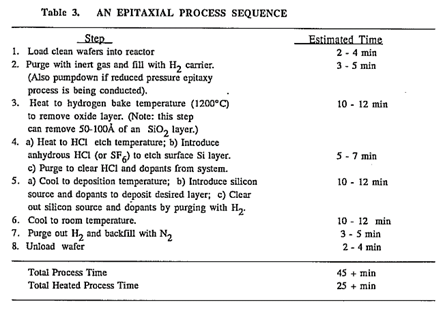

最后,贴一张典型的EPI recipe架构吧,大家学习一下。机台的话以前是桶式的(batch run),但是均匀性不好。现在都是单片的chamber了,ASE2000机台,量测的话主要是FTIR量厚度,用C-V量阻值。

收工前,照例分享两篇经典EPI材料吧:

1. <Silicon Epi by Chemical Vapor Depsition>: http://pan.baidu.com/s/1pJmSb5D

2. <HCl&Cl2 clean before Epitaxial>: http://pan.baidu.com/s/1c0yJJ3a

支付宝打赏

支付宝打赏  微信打赏

微信打赏