栅极材料的革命 (Gate Electrode) (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

半导体制程技术的发展最为曲折离奇的故事应该算是栅极了,从MOSFET (Metal Oxide Semiconductor)的第一个字母我们就知道曾经的曾经这个栅极材料还是Metal Gate呢,可是现在8寸的主流又是Poly Gate了,到了12寸的45nm以下又还原到Metal Gate了,真正上演了佛家的前世轮回因缘理论。

今天,我们就来讲讲栅极氧化层以及栅极材料的革命发展史,以及其中遇到的问题都是什么?

上个世纪70年代,MOSFET (MOS场效应晶体管)刚出来的时候结构非常简单,我十年前有幸做过2.25um的Metal Gate,工艺流程就是N/P WELL、N+/P+_S/D、GOX、CONT、METAL1、Passivation就结束了。

简单吧!但是这个Vt真心不好做,比现在的Buried Channel的PMOS还难做,主要涉及低温沉积AlSiCu否则很容易引入Surface Charge (Qss)。而且对于Metal Etch的Power、RF要求非常高,Metal蚀刻之后还要有一步 soft Etch,否则无法去除Metal Etch留下的Si residue (6寸时代因为Al穿刺问题,Target里面是含有1%的Si的)。

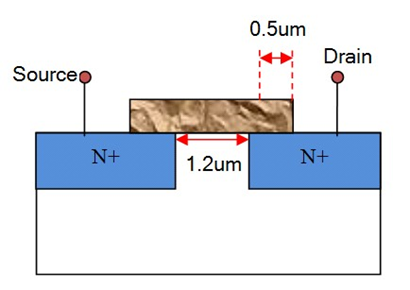

看flow的顺序就可以看出它是先做N+和P+的Source/Drain并退火激活,再去做Metal1的Gate,所以Metal1要确保能够接触Source/Drain,就必须留够Overlay (rule规定为0.5um)。但是这样的Overlay在性能上是无法接受的,太浪费面积而且Overlay电容太大,GIDL(Gate Induced Drain Leakage)漏电也会很大。所以后来发展到先做Gate再做Source/Drain,这样就可以自对准了,但是问题又来了,Source/Drain的掺杂必须要经过800C以上的高温激活,这Metal Gate的AlSiCu就没法承受了(熔点450C),所以不得不寻求新的Gate Material,也就是我们现在用的Poly Gate。(2um以前的时代都是Metal Gate,1.5um以下的时代都是Poly Gate了)。

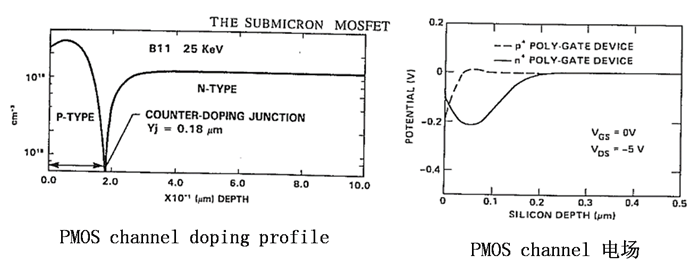

而Poly Gate本身也是一波三折,最早用PolyGate的时候Poly都是Doped Poly (540~560C),直接在deposition的时候in-situ通入了PH3掺杂,或者后面用POCl3掺杂,一直持续到8寸的0.35um CMOS时代。但是这种Poly的问题是什么?由于掺杂可以改变半导体的功函数(work function),通常N-Si和P-Si的功函数差0.5~0.7V,而我们的Poly是N-Poly,它和PWELL的功函数以及与NWELL的功函数差约0.6V,虽然可以通过Vt_imp来拉平,而这个VT_IMP需要打入Boron来抵偿。但是这样的问题会导致埋沟器件(buried channel PMOS, BC-PMOS),机理是因为打入的Boron使的它与NWELL形成了一个一定深度的PN结,而这个PN结导致了电场最小的位置发生了变化,由原来的沟道表面(Near GOX)转移到PN结处,而这样带来的问题是该PMOS的在电势最小的PN结处容易发生源漏的空穴注入导致空穴载流子迁移率增加的问题(15% higher),因为沟道里面不是原来的N型而是轻微掺杂的P型,所以从源漏极与沟道的PN结隔离壁垒就减弱了,所以发生了空穴注入效应导致Vt降低,俗称Vt Roll-off。而BC-PMOS的Vt roll-off更敏感,以前的做法是故意把PMOS做大一点,但浪费空间,所以后来都是靠process去control Vt variation,这就是为什么我们都在complain 0.35um的PMOS Vt比较难做。(那些不懂事的老板或者PE们总说0.35um Vt的sigma还比0.18um的差,你们怎么做的?只能嗤之以鼻,不想对牛弹琴了)

再回来讨论Poly gate吧,刚刚讲的如果直接在poly gate沉积的时候掺入N+,这样PMOS就比较难做了,尤其到了0.25um已经无法接受了,所以后来人们直接把doping拿掉了(温度还是540~560C, Amorphos poly),靠源漏注入(S/D_IMP)来顺便给Gate掺杂了,这样的话NMOS的Gate就是N-poly了,PMOS的Gate就是P-Poly了(也叫双Gate,或dual gate electrode),本身就消除了功函数差异带来的Vt差异了。(这样的问题是Gate Poly的阻值无法降下来,不过后面有了Ti-Silicide/Co-Silicide可以解决这个问题)。但是后来又发现Gate poly掺入了源漏注入的Boron很容易发生Boron沿着晶格间隙(Grain boundary)扩散进入GOX和衬底而导致Vt变化,所以后来到0.18um时代Poly的沉积温度又变为620C~630C,这样可以减小晶格大小(Grain size),抑制了Boron穿透效应(Boron penetration)。(当然GOX也有改进掺入N2O生成含N的Oxide,一方面提高GOX的节电常数一方面抑制B-penetration)

至此,PolyGate的革命算是走向成熟了,所以说PolyGate几乎统治了半导体栅极革命的数十年整个"亚微米时代" (Sub-Micron era),到半导体进入到纳米时代,则栅极革命又面临新的问题了。

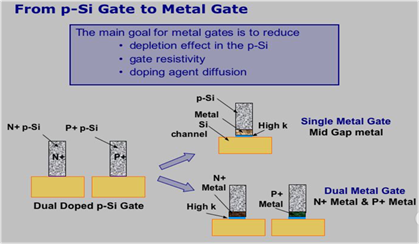

我们知道栅极的Poly是需要通过掺杂(doping)来降低阻值的,但是这样的doping在栅极电压下会发生doping浓度的变化,比如N-poly的NMOS加正电压,则N-type载流子会受Gate电场向上再分布,导致底部的N-几乎都被电场拉走而变成不导电的Silicon,而这一部分不导电的Silicon自然就被算入栅氧化层的厚度,导致有效栅氧化层厚度变厚(EOT: Equevalent Oxide Thickness),这就是大名鼎鼎的多晶耗尽效应(PDE: Poly Depletion Effect)。当器件进入45nm以下时,这样的多晶耗尽会导致有效栅氧电性厚度升高,所以Cox下降,所以栅极跨导降低,减弱了栅极对沟道载流子的控制能力,所以为了避免这种情况的发生,不得不继续迂回走入Metal Gate。所以我们经常看到很多公司介绍他们的制程为28nm HKMG,这里的“HK”当然就是Hi-K高介电常数,而“MG”就是Metal Gate。

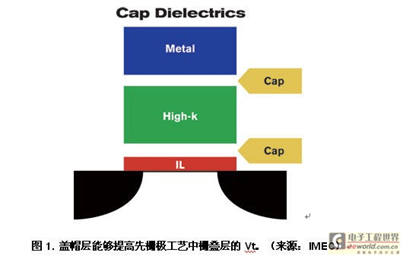

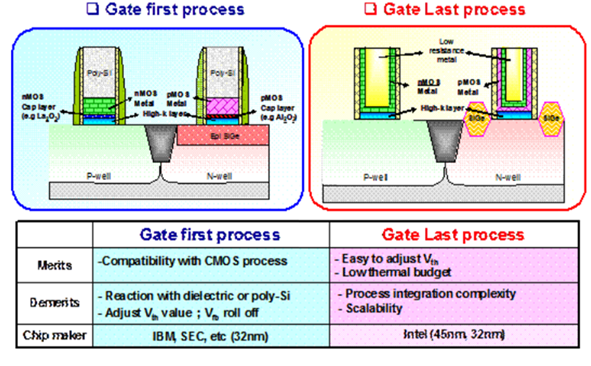

那问题又回到半导体发展20年前的问题,MetalGate的问题是与源漏极的交叠问题,纳米时代肯定不能容忍交叠电容(OVL Cap)的R*C delay,所以除非你还是坚持先做MetalGate再做源漏极,那你的MetalGate必须的撑得住高温的源漏退火激活(比如TiN或者WSix都可以)。所以好多公司坚持先做Gate再做源漏,这就是著名的栅极优先理论(Gate-First),它的创始者是IBM公司,追随者有英飞凌、NEC、GF、三星等。它的优点是制程的flow几乎沿用传统的PolyGate工艺,所以寄生参数等特性变化比较少,设计者几乎不需要做太多的变化。但是Gate-first的缺点还是功函数差而导致的PMOS Vt的问题,所以需要在NMOS的栅极介电层(不能用氧化层咯~)cap一层<1nm的La2O3,而在PMOS上cap一层Al2O3,但是这就多了一道Dual-Gate Photo/Etch,而这道process的蚀刻和去光阻对NMOS上的介质层厚度的控制非常敏感,尤其是去光阻设备的挑战。

所以说在Vt的要求还不高的情况下,可以勉强使用Gate-First。所以以Intel和tsmc为先的业界老大,最早在45nm的时候就开始直接开发后栅极(Gate-Last)工艺,Gate-Last可以更好的控制栅极材料的功函数,而且还可以方便引入改善沟道载流子迁移率的应变硅(Strain Silicon)工艺,非常适合低功耗和高性能应用,老大就是老大,策略和眼光更长远,所以后来三星也转型了,IBM和GF在32nm以下也不得不走入咱的阵营了。当然Gate-Last的问题就是OVL问题了还有就是器件结构变了,设计变更会比较大,OVL问题交给ASML光刻机吧,都纳米时代了,它的对位总不能还依赖process自对准吧。设计问题只能设计公司自己解决了,性能是需要付出代价的,除非有人Gate-first性能超越咱~~。

至此栅极革命告一段落,如果有缘期待退休前能看到下一次革。

支付宝打赏

支付宝打赏  微信打赏

微信打赏