栅极介质层的变迁(Gate Dielectric) (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

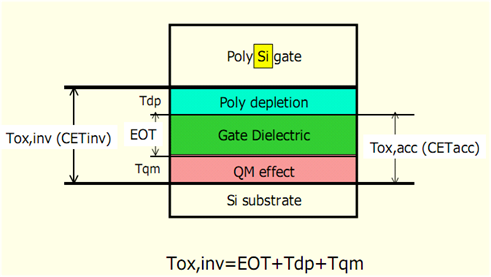

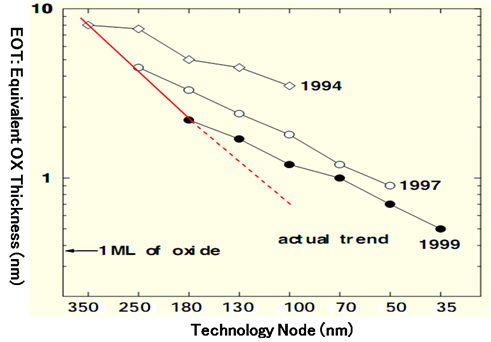

昨天已经讲完了栅极材料的演变(Gate Electrode),当然伴随它一起的自然就是栅极介质层(Gate Dielectric),记住我讲的是栅极介质层,不是我们平常讲的栅极氧化层(Gate Oxide),早期我们讲的MOSFET的介质层就是我们狭义讲的Oxide,但是随着Moore's Law的scale down,我们需要不断的降低我们的oxide厚度来换取低的开启电压(栅极跨导),换言之也就是要更高的栅极电容来耦合,但是无限制的减薄GOX厚度势必造成漏电和击穿等问题,所以必须寻找新的栅极介电材料来提高击穿电压减小栅极漏电流。今天我们就来讲讲栅极介质材料的那些事吧!

最早期的微米以上的制程比较容易理解,就是用SiO2 (oxide)来做栅极氧化层这也是半导体发展的这半个世纪的主流,当然从微米制程发展到亚微米制程以及到后面的深亚微米围绕GateOX的process经历了不同的制程演变。

学校的教科书里面,我们一直都在讲氧化层质量最好的一定是干氧(Dry oxide),因为每个二价的氧外面一定有两个硅原子,每个硅原子外面有四个氧原子形成的稳定的桥连氧结构(Bridge oxide),质量次之的当属湿氧(Wet Oxide),因为很多“硅-氧”键会被打断并由“H”取代,所以oxide的结构相对疏松。当然我这里不会去具体讲干氧和湿氧以及氧化制程的原理了,大家可以参阅前面的topic有详细介绍。(http://ic-garden.cn/?p=403)

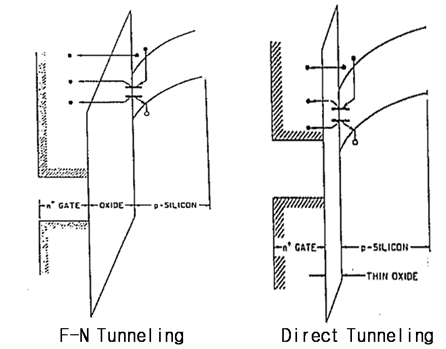

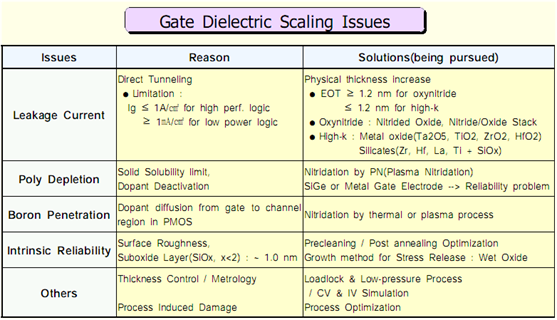

而半导体最初期的制程的栅极介质层就是沿用了书本的理论用的是干氧(Dry Oxide),因为那个时候的栅氧普遍比较厚几乎都在100A以上,GOX本身的质量占主要地位。可是到后来我们到3.3V以下,进入到50A的GateOX的时候,栅极氧化层的tunneling就会变得不可忽略,主要有两种tunneling,一种叫做F-N tunneling (Fowler-Nordheim),一种叫做Direct tunneling。前者F-N tunneling指的是电子通过三角形的能带势垒穿透进入氧化层的导带,然后在Gate电场下形成栅极漏电流。而这种F-N tunneling主要和Si-SiO2的界面陷阱有关,实际情况在正常器件工作下,F-N tunneling不会造成足够的电流导致器件烧毁,所以即使在深亚微米时代(70A)时候,依然可以继续沿用 (但是作为Flash的tunneling是不可以的,必须>90A)。第二种tunneling:direct tunneling是当GOX足够薄到<50A以下的时候,沟道表面的电子在电场作用下可以直接穿过氧化层的禁带(Forbbiden band),而不是先进入导带,从隧穿能带图看出它也是隧穿无需辅助能级直接穿透以及界面陷阱辅助。所以无论从F-N tunneling还是direct tunneling都有一个直接的问题就是界面陷阱能级,而这个界面陷阱能级主要来源就是界面被打断待反应的Si-键因为没有氧与之键合形成桥连氧而变得非常活跃容易俘获电子成为漏电源,所以这个硅键被称之为悬挂键(Dangling bonds)。为了解决Dangling bonds的问题,所以引入了湿氧(Wet oxide),因为湿氧含有氢键(H+),比较容易穿透Oxide film进入界面填补悬挂键解决界面陷阱问题,同时湿氧(Wet Oxide)因为Thermal budget比较少,比较适合Advance制程的需求。

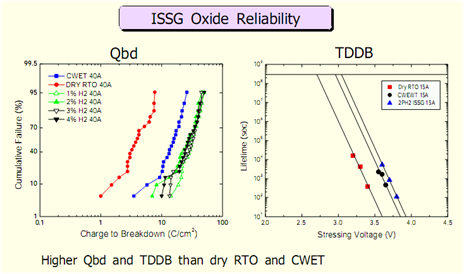

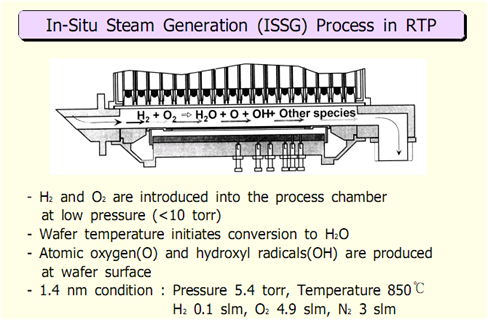

说起湿氧(Wet Oxide),也别有一番动人的故事,最早期在48A, 32A以及26A的时候几乎都还是传统的Wet Oxide,就是在炉管里面通入H2和O2燃烧后的水蒸汽进入管子里与硅反应 (记住不是直接通水汽哦,因为杂质太多不够纯)。可是到了20A以下几乎很难再用炉管来长了,因为炉管进去出去都得半天,这过程都可以长20A的自然氧化层了,根本无法控制,而且用炉管长你肯定的用低温吧,那你的Quality怎么保证呢?所以后来发展到Wet-RTO,RTO(Rapid Thermal Oxidation)可以在数秒内高温下完成Oxidation,因为时间短所以整个thermal budget是可以接受的,而且温度高(>1000C)的Oxide quality也是可以保障的,同时可以抑制Boron Penetration。而这个Wet-RTO现在业界主流还是用AMAT (Applied Material)公司的ISSG (In-Situ Steam Generation),据传它用湿氧长出来的GOX的quality可以媲美Dry oxide。

说起这个ISSG (In-Situ Steam Generator),它与普通RTO的区别是低压(low pressure)冷壁(cold wall)的RTP反应腔体。低压主要是安全问题防止爆炸而且降低气压也可以降低反应速率提高均匀性和quality,而冷壁主要是因为防止Torch里的石英管壁分解散发一些物质进入GOX里。所以不仅仅在20A可以用在一般的30~50A如果特别care GOX quality的technology也可以使用,只是cost要balance。

在Gate Oxide制程里面还有一个很重要的概念就是氮化(Nitrided)和氟化(Fluorinated),当栅氧厚度发展到40A以下的时候,GOX的很多问题还包括Boron penetration、栅氧击穿/漏电、热载流子注入损伤等,所以在ISSG出来之前迫切需要提高炉管的GOX的quality,所以引入了氮化的二氧化硅(Nitrided SiO2),其实就是类似Oxynitride,在GOX里面引入1~2%原子百分比的N原子以减少固定氧化物电荷,5%的氮原子可以有效减少Boron penetration。早期的氮化制程采用的是NH3,但是容易引入固定电荷(fixed charge, Qf),所以后来普遍采用N2O制程,当然N2O的GOX制程也不是万能的,它也有界面问题、固定电荷问题、以及降低mobility和反应速度慢等问题,所以还是要引入最后的ISSG制程。引入Fluorine的主要作用就是做为反应催化剂提高速率,另外氯(Cl)可以钝化金属元素。

下面再来讲讲Advanced制程的Gate Dielectric吧,当制程进入到纳米时代,如果我们继续使用SiO2,那么我们还能继续down薄吗?已经~15A了,就直接隧穿了(Direct Tunneling)。当然我们的制程工程师已经努力尝试各种方法希望继续沿用SiO2,因为它和硅/Si已经多晶最为接近应力最匹配,但是已经极限了无能为力了。所以我们不得不引入Hi-K栅极介质层(k>=7,OX's k=3.9),这样我们就能够提高栅极介质厚度来避免direct tunneling,并能继续维持高的Drive-current (or Transconductance,跨导)特性,从开启电压的公式我们也可以得出栅极电容才是主要dominate的因素。

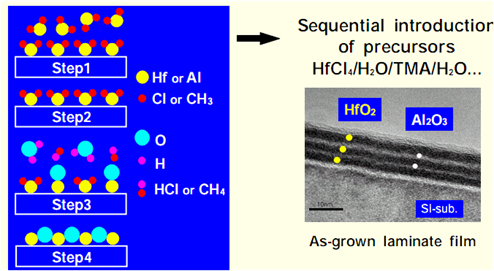

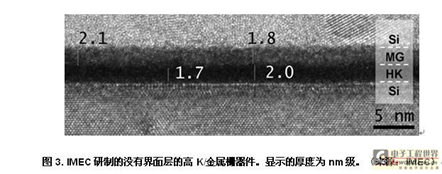

在Hi-K的选择上,早期65nm到45nm时代都是采用HfO2和Al2O3的组合叠层(HfO2-Al2O3 Laminate),主要考虑这两层film的互补问题,应力互补而且前者含有positive Fixed charge而后者含有Negative Fixed charge,所以刚好互补。主要采取的制程方法都是用ASM公司的ALD (Atomic Layer Deposition),因为更好的厚度均匀性控制、particle、step-coverage、Low Thermal budget等优势。在反应之后需要进行N2环境的RTA treatment,让两层film反应最终生成HfAlO介质层。

到45nm制程以下的32nm或28nm等,目前我还不知道用什么材料,但是有介绍说因为32nm和28nm由于用了Metal Gate,他们存在了功函数(work function)差,所以必须要在Hi-K介质上各自Cap一层氧化层来balance NMOS和PMOS的功函数差,NMOS上要用La2O3,PMOS上用Al2O3,厚度均小于10A。厚度之薄令人叹为惊人!

然而Hi-K介质层也并非好到非常好,不然当初科学家们也不会选用SiO2了,有何问题?首先与SiO2相比,它与Si制程比匹配,因为SiO2的各项物理特性都和Si是接近的,工艺是兼容的。还有一个问题Hi-K肯定应力大(如Si3N4),所以界面陷阱电荷(Dit)以及固定电荷(Qf)都变高。最后一个问题是Hi-K的应力会让晶格变化导致载流子迁移率降低,所以需要引入Strain-Silicon (Ge) or Poly-SiGe结构提高载流子迁移率。

每次新材料的变革将会是颠覆性的,所以我们的制程工程师总是想方设法能够沿用原有的材料如同SiO2时代,所以一样的业者应该会继续努力提升HfO2特性确保不要那么快被新的材料取代,而我们任何两种不同的材料接触都会产生界面层(IL),而当我们厚度继续down薄到10A的时候,而界面层厚度为5A的时候,那我们的界面层是不是致命的?所以在改善介电常数的同时,我们还要减少界面层(IL),SEMATECH以及IBM等公司都宣称可以制作零界面层的介质层(ZIL: Zero Interface Layer),但是零界面层通常需要高温化学反应来消除,所以它不利于Gate-Last制程而有利于Gate-First,如果真能实现的话估计Gate-First将会赢得市场,当然前提是要快,否则设计都转过去想转回来又不可能了。不过如果Gate-Last制程里面能够不需要高温就能够有效去除界面的氧离子达到消除界面层的目的,那真真也是极好的。

最后栅极介质层有个特性叫做应力导致漏电流(SILC: Stress Induced Leakage Current),它是指薄GOX在高电场下产生中性的氧化层陷阱(neutral oxide-traps)导致电子隧穿(electron tunneling)。在厚栅氧时候它是瞬态的,在薄栅氧时它是持续的,通常它主要是非挥发性存储器data retention和program/erease不达标以及soft breakdown的主要原因。

后面,再设专题讲解Gate Dielectric的电荷以及电容特性吧~

分享一篇文章:http://pan.baidu.com/s/1qW9l08s

Hi-K/HfO2 Characterization: http://pan.baidu.com/s/1mgjBm5q

支付宝打赏

支付宝打赏  微信打赏

微信打赏