IGBT理论与实践–实用篇 (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

之前发了一篇关于IGBT的文章--“大功率器件-《从PowerMOS到IGBT》”,今年一下子火了。所以趁热打铁吧,继续来点干货吧。

资料比较零散,想到哪写到哪,但是绝对没有废话。实在是工作生活都很忙,没时间搞那些排版什么的,大家将就看了啊。

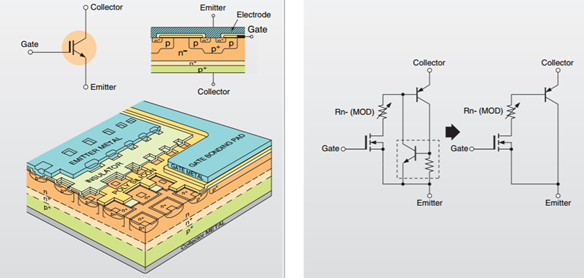

回顾一下IGBT的工作原理,首先Gate控制MOSFET导通,产生Drain-to-Source的电流,而这个电流同时也是BJT的基区电流(Ib),而Ib*Rb就是BJT的Vbe,所以只要MOSFET一旦turn-on,这个Vbe一定很容易就大于0.7V了,所以这个BJT的Vbe就导通了,此时BJT管就导通进入放大区了(发射结正偏,集电结反偏)。

IGBT里面有一个天然寄生的NPNP晶闸管,这个和CMOS的闩锁效应一个道理。所以需要分别控制两个BJT的Gamma(共发射极电流放大系数),最好的方式就是Vbe短接,这就是为什么IGBT都需要把contact从Emitter延伸到Body里面去。

首先,我们看到比较多的都是N型IGBT,那么有没有P型IGBT?答案肯定是有,为啥不用呢?其实就是跟CMOS之前一样,为啥只有NMOS?因为PMOS电阻大啊!同样的道理,P-IGBT的on-state阻抗太高,Switch loss太高。而且P-IGBT更容易Latch-up,也就是SOA太窄了。

一般评估Power Device的特性的重要参数:

1、Voltage Rating: 关闭状态下的阻挡电压的能力,过压损坏;

2、Current Rating:导通状态下传输电流的能力,功率过高或者结温过高都会损毁;

3、Switch Speed:电流和电压改变的速率,决定了开关损耗。

4、On-State Voltage:决定了导通状态的损耗;

而对于IGBT来讲,Voltage Rating几乎在几百伏到3000伏以上,甚至现在有4、5千伏了。而Current Rating几乎可以到1200A了(同时并联几个)。而switching speed可以到3万Hz。

Planar IGBT过度到Trench IGBT一方面是面积节省,另一方面是Planar-IGBT多了个寄生的JFET,使得载流子浓度降低,所以Ron降低以及Switch速度下降,还有SOA也变窄。

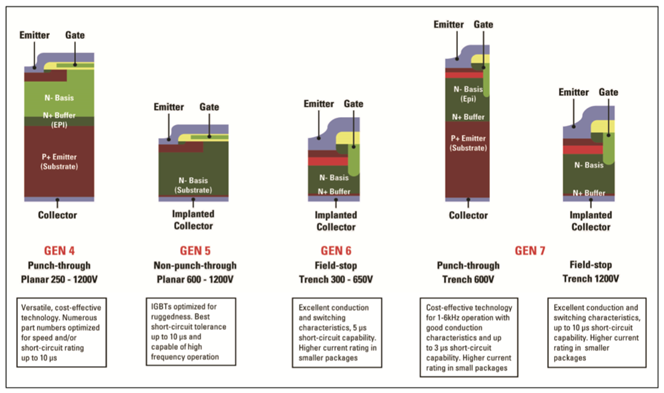

在上一篇文章里面已经讲过PT-IGBT和NPT-IGBT了,PT-IGBT在off-state的时候BVCES耗尽整个N-区达到N+,N+/N-的浓度差会抵消剩余电场达到耐压的目的(Prevent "reach-thru", Vce),所以可以通过降低N-浓度或EPI厚度来达到Low Vce(on)和High BVCES的trade-off。

和之前一样,N+ buffer的作用是提供源源不断的电子来阻止Hole injection,提高switch speed。PT-IGBT也有增加表面contact P+ implant增加P-Body的pick up能力,提高NPN管的Vbe shortening,提升SOA。

那么PT-IGBT基本上还是用EPI做的,电压处于中低压(<=600V),这对于BV和Vcesat来讲性能都不错,但是电压再往上就不行了,因为EPI需要继续增厚,很难长那么厚的defect-free的EPI。(PSUB->N+_IMP->EPI)。而且PT-IGBT需要在N+ buffer层上长EPI,auto-doping (自掺杂)效应引入大量少子,会导致Turn off速度变慢,导致switch loss太大,frequency也降低。

再来,NPT-IGBT。更厚的N-肯定不能用EPI了,所以必须实用FZ wafer了,背面用shallow P+ implant,深度和剂量都会影响PNP管的hole injection能力。

PT-IGBT是靠N+ buffer去kill hole提高speed,而NPT-IGBT增势靠precise control背面P+ implant来控制hole injection,当然NPT-IGBT还是需要N+ implant的,只是作用不做buffer了,而是做field stop。

Trench IGBT除了提高cell密度,还减少JFET电阻,而Planaer IGBT由于电流拥挤以及电场线分布等问题,都会发生在P-well的转角处,所以Pwell的间距一定要卡好,否则无法产生BJT的电导调制效应。

在Off-State的时候,这时候关键是BVCES,常规理解是跟N- Thickness有关,也就是漂移区长度。除此之外,他还跟Poly Gate width有关(Cell之间击穿),还有P-body的宽度、深度、浓度等导致电场线弯曲和穿通等问题,还有Trench自己的深度、宽度、间距以及coner rounding都会有影响的。

在On-State的时候,主要就是导通电阻Ron了,按照电流公式Ic(sat)=Gm*(Beta+1)*(Vge-Vt)^2。这里Gm就是MOSFET的跨导(与Cox, μn, W/L)。而Beta则与N-漂移区的少子寿命,N+ buffer的profile有关,一般为了好的开关速度都希望少子寿命比较低,所以Beta也就被降低了。

另外在ON-State下的Vce(on)与速度强相关,同时他也决定了ON-State的功耗。Vce(on)=Vce(offset) + V(N-region) + Vds(Surface MOSFET)。其中,Vce(offset)就是collect区的欧姆接触电阻相关,Vds与Cell密度相关,最复杂的是V(n-region)这是BJT的电导调制效应,但是靠hole inject调制又会使得turn-on/off速度变慢,所以IGBT的速度总比MOSFET慢,这也算是Speed与Vce(on)的折衷吧。(NPT-IGBT没有N+ buffer,没有了life killer了,所以他的速度可以达到100~300nsec)。

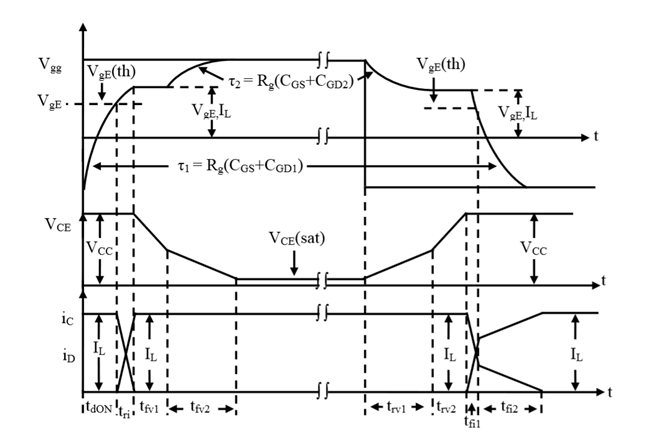

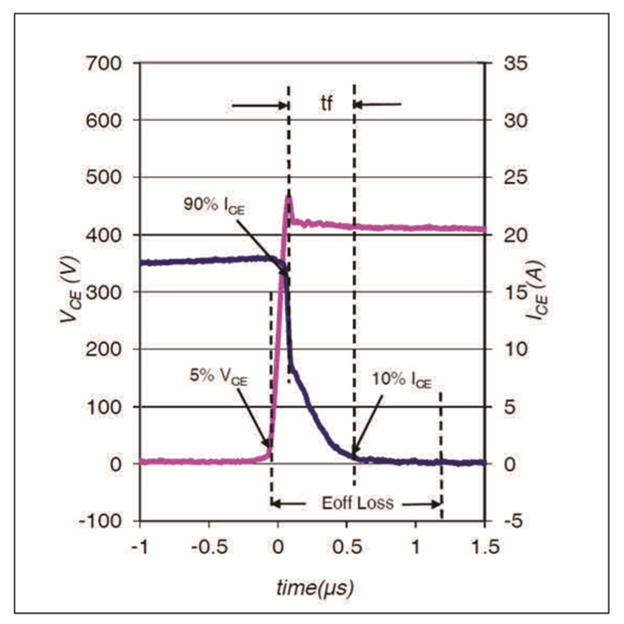

再来个switch的特性,Turn-on开启损耗(Eon)与电压从Vce下降到Vce(on)的时间(Tfv)有关,而Tfv又正比例于少子寿命以及PNP的Beta。一般情况降低lifetime的方式是引入重金属掺杂或者高能辐照,而Beta的降低可以通过N+ Buffer浓度提高(PT-IGBT)或降低背面P+的浓度来实现。

上面的总结有MOSFET的Gm和Vce(on)有关,所以我们希望Vce(on)小一点,那就Gm小一点(Cox小一点),但是这和MOSFET的特性又不符合(Cox小可靠性就差了,动态特性也不好),所以这里也是一个折衷选择。

不管是开启(Switch)还是关断(Fault)下,Ic和VCE都是同时存在的,这会有SOA问题(是指附在线可以在指定的结温和脉宽下跨过整个器件的工作特性曲线)。BJT有两个SOA:FBSOA(正偏)和RBSOA(反偏),如果Base是floating的则IGBT的RBSOA可以忽略。

一般FBSOA有两种失效机理:电流失效和电场失效,前者是过量的空穴在P-body里导致NPN的Vbe正向导通产生Latch-up,而后者过量的电荷累计导致N-耗尽层变窄而穿通。(还有一种是短路SCSOA,我不太知道了。)

分享一些资料大家自己下载学习吧:https://pan.baidu.com/s/1i6A08Rj

支付宝打赏

支付宝打赏  微信打赏

微信打赏