Moore’s Law: 浓缩就是精华!(转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

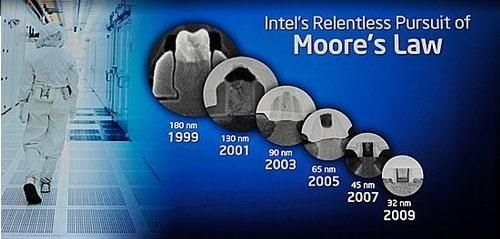

但凡对半导体这个行业有点了解的,应该都懂摩尔定律(Moore's Law),这也是个魔咒。这是70年代Intel创始人Gordon Moore在60年代提出来的黄金定律,被业界遵循为黄金定律,也是从那个年代开始我们世世代代的半导体人都为之疯狂,这就是为什么这个行业的人压力那么大的原因。

--Small is Beautiful!浓缩就是精华!

说起摩尔定律,大家一定比我会背:每18个月(后来修正到18~24个月),单位面积的晶体管数目需要增加一倍,当然换算到Cost就是降低一半了,曾经有人无聊的算过一笔账,如果按照摩尔定律的速度,现在那些奔驰宝马也就几分钱。但是你知道这个定律的描述如何和我们的0.5um、0.35um、0.25um....90um、65um、45nm、28nm等关系吗?我们每个节点都是一个generation,而每个generation如何实现面积减小一半?因为我们需要面积缩小一半,也就是50%,那样边长需要缩小多少?是不是70%?这样才能70%*70%从而达到50%的面积节省,所以就有了0.5um*70%到0.35um,0.18*70%=0.13um就这么来的,简单吧。

点击阅读全文

《Moore’s Law: 浓缩就是精华!(转)》.doc

将本文下载保存,方便收藏和打印

导出文档