FinFET简介(转)

FinFET

FinFET简介

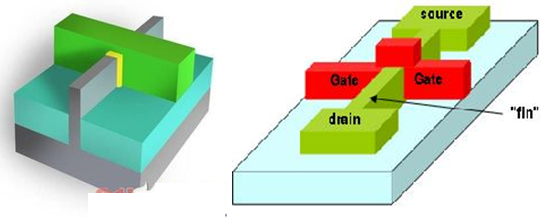

FinFET称为鳍式场效晶体管(FinField-EffectTransistor;FinFET)是一种新的互补式金氧半导体(CMOS)晶体管。闸长已可小于25奈米。该项技术的发明人是加州大学伯克利分校的胡正明教授。Fin是鱼鳍的意思,FinFET命名根据晶体管的形状与鱼鳍的相似性。

该项技术的发明人是加州大学伯克利分校的胡正明(ChenmingHu)教授[1]。胡正明教授1968年在台湾国立大学获电子工程学士学位,1970年和1973年在伯克利大学获得电子工程与计算机科学硕士和博士学位。现为美国工程院院士。2000年凭借FinFET获得美国国防部高级研究项目局最杰出技术成就奖(DARPAMostOutstandingTechnicalAccomplishmentAward)。他研究的BSIM模型已成为晶体管模型的唯一国际标准,培养了100多名学生,许多学生已经成为这个领域的大牛,曾获Berkeley的最高教学奖;于2001~2004年担任台积电的CTO。

英特尔公布的FinFET的电子显微镜照片

FinFET闸长已可小于25纳米,未来预期可以进一步缩小至9纳米,约是人类头发宽度的1万分之1。由于在这种导体技术上的突破,未来芯片设计人员可望能够将超级计算机设计成只有指甲般大小。FinFET源自于传统标准的晶体管—场效晶体管(Field-EffectTransistor;FET)的一项创新设计。在传统晶体管结构中,控制电流通过的闸门,只能在闸门的一侧控制电路的接通与断开,属于平面的架构。在FinFET的架构中,闸门成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。这种设计可以大幅改善电路控制并减少漏电流(leakage),也可以大幅缩短晶体管的闸长。[2]

在2011年初,英特尔公司推出了商业化的FinFET,使用在其22纳米节点的工艺上[3]。从IntelCorei7-3770之后的22纳米的处理器均使用了FinFET技术。由于FinFET具有功耗低,面积小的优点,台湾积体电路制造股份有限公司(TSMC)等主要半导体代工已经开始计划推出自己的FinFET晶体管[4],为未来的移动处理器等提供更快,更省电的处理器。从2012年起,FinFET已经开始向20纳米节点和14纳米节点推进。

FinFET和普通CMOS的区别

CMOS(ComplementaryMetalOxideSemiconductor),互补金属氧化物半导体,电压控制的一种放大器件。是组成CMOS数字集成电路的基本单元。

在计算机领域,CMOS常指保存计算机基本启动信息(如日期、时间、启动设置等)的芯片。有时人们会把CMOS和BIOS混称,其实CMOS是主板上的一块可读写的RAM芯片,是用来保存BIOS的硬件配置和用户对某些参数的设定。

在今日,CMOS制造工艺也被应用于制作数码影像器材的感光元件,尤其是片幅规格较大的单反数码相机。

SOI和体硅FinFET的比较

本文比较了SOI和体硅FinFET器件在性能、加工工艺及其成本上的差异。如果要使SOI和体硅的FinFET器件具有相类似的性能,体硅FinFET器件的制备流程将更为复杂。在SOI晶圆上,氧化埋层隔离了分立的晶体管,而在体硅器件中,隔离作用则必须通过晶圆工艺来形成。我们将证明,由于体硅FinFET工艺更为复杂,使得器件的差异性达到SOI的140%~160%,并会对制造和工艺控制产生严峻的挑战。虽然SOI基片更为昂贵一些,但更为复杂的体硅FinFET工艺成本的增加大体上已抵消了这部分开销,从而使得在大批量生产时其成本能与体硅工艺大体上相当。

HoracioMendez,SOIIndustryConsortium,Austin,Texas,USA;DavidM.Fried,IBM,EastFishkill,NYUSA;SrikanthB.Samavedam,FreescaleSemiconductor,EastFishkill,NYUSA;ThomasHoffmann,IMEC,Leuven,Belgium;Bich-YenNguyen,Soitec,Austin,Texas,USA

当半导体业界向22nm技术节点挺进时,一些制造厂商已经开始考虑如何从平面CMOS晶体管向三维(3D)FinFET器件结构的过渡问题。与平面晶体管相比,FinFET器件改进了对沟道的控制,从而减小了短沟道效应。平面晶体管的栅极位于沟道的正上方,而FinFET器件的栅极则是三面包围着沟道,能从两边来对沟道进行静电控制。

3D结构的挑战

3D结构将会产生新的寄生电容和特征尺寸,这些都必须加以控制以优化晶体管的性能。FinFET器件的栅长是在平行于“鳍”方向的长度,而沟道的宽度是两倍于“鳍”高度再加上“鳍”的宽度。“鳍”的高度限制了驱动电流和栅电容,而“鳍”厚度会影响到对阈值电压和短沟道的控制,还会影响到其二级效应,如功耗。

在一个22nm技术节点的器件中,“鳍”宽度可能为10~15nm范围,理想的“鳍”高是宽度的两倍或更多,因为增加“鳍”的高度可以提高晶体管的集成密度,以在更小的占位面积上形成更大的有效栅宽。然而,对体硅FinFET器件而言,更高的“鳍”使得对“鳍”的刻蚀、“鳍”壁的凹槽刻蚀,以及隔离注入变得更为困难,这些将在下面的文章中进行讨论。

在器件的制造中要控制如此小尺寸的3D结构,这就给工艺控制带来新的挑战。构建“鳍”结构的沟槽刻蚀,必须保持好2:1或者更大深宽比结构的垂直轮廓,使其边墙具有最小的粗糙度。差异性及良品率问题是制造厂商决定采用哪种制备工艺的重要考虑因素。

本文将分析两种具有应用前景的FinFET工艺流程的性能、差异性及其成本,其中一种是采用绝缘体上硅(SOI)基片,另外一种是使用离子注入形成PN结来进行“鳍”隔离的体硅基片。

采用SOI基片的工艺流程。基于SOI的FinFET工艺最为简单。形成“鳍”的刻蚀过程将会在进行到晶圆氧化埋层时自动中止,“鳍”的高度将完全取决于初始SOI上Si层的厚度。此外,由于存在着氧化埋层,相邻的“鳍”之间在电学上是完全隔离的,不需要再进行额外的隔离工艺。在全耗尽的情况下,该技术节点将考虑采用未经掺杂沟道的器件,因而只需要制作栅极并对源/漏进行注入掺杂就可以完成整个器件的制造工艺。

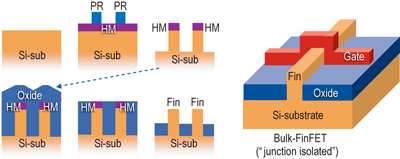

采用体硅基片的工艺流程。与SOI相比,如果采用体硅基片,就无法在“鳍”的底部形成清晰的界面,而且不存在本征隔离层(氧化层)。因而就必须采用额外的器件隔离工艺。在形成PN结隔离的工艺流程中(图1),完成“鳍”的刻蚀后紧跟着要进行氧化物的填充步骤。氧化物要能够很好地填充很深的、且深宽比大的沟槽,要保证不产生孔洞和其它类型的缺陷。随后磨削抛光氧化物直至硅暴露,以确定“鳍”的高度,再进行对氧化层进行凹槽刻蚀以便在“鳍”之间清理出空间。这种氧化层凹槽刻蚀和最初的硅沟槽刻蚀相类似,都没有明显的刻蚀终止层,其刻蚀深度完全取决于刻蚀的时间,随着设计中“鳍”间隔变化而使“鳍”密度发生变化时,刻蚀就会受到微负载(图形)效应的影响。虽然填充的氧化物会将相邻的“鳍”绝缘隔离,但是晶体管依然可以通过氧化物下部的硅衬底相连,这就需要通过高剂量的、大角度离子注入以在“鳍”的底部形成掺杂PN结,才能最终形成器件的隔离结构。

图1.采用PN结隔离的体硅FinFET器件的工艺流程。

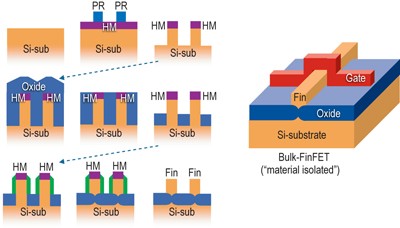

“材料隔离”工艺流程。一些研究还在考虑采用“材料隔离”工艺(图2),在该工艺中,氧化物从沟槽向“鳍”的底部生长并穿透形成隔离,需要采用一种硬掩模边墙来保护“鳍”的两壁。在这种工艺中,氧化物生长程度取决于其生长的时间,这就要求所有的“鳍”都必须具有相同的厚度,才能形成完全的氧化物隔离。氧化物隔离生长过程本身就非常难以控制,而且与PN结隔离工艺相比还增加了多个工艺步骤。由于其自身的复杂性,我们认为“材料隔离”方法在实际生产中并不可行,所以在随后的分析讨论中我们将不再考虑这种工艺。

图2.“材料隔离”体硅FinFET器件的工艺流程。

SOI和体硅工艺都可以达到类似的性能

对于器件的直流DC性能而言,尺寸类似的SOI和体硅FinFET器件可以获得相似的开/关电流比[1]。但在考虑PN结漏电流和寄生电容等参数时,两种器件的表现就会开始显现出差别。由于SOI本身就具有底部的平面氧化层,使其更容易实现22nm技术节点器件的目标性能。

正如前面所述,在采用PN结进行隔离的FinFET器件中,其隔离是通过在“鳍”底部形成高剂量(1018/cm3)的掺杂层来实现的。该掺杂层可以在凹槽氧化物淀积和刻蚀之前或者之后通过离子注入形成,但在PN结和氧化层之间的对准就变得至关重要,它对器件性能的影响与平面晶体管中边墙-沟道间的对准要求相类似。

在凹槽氧化物淀积和刻蚀之前就进行离子注入会放大凹槽刻蚀的非均匀性,从而对器件性能产生影响,而凹槽刻蚀工艺步骤的本身就已经是一个技术上的挑战。所以,为了能商业化应用大多数工艺考虑都先进行氧化物淀积和刻蚀,使用氧化层来对准PN结的离子注入。即使是采用这种工艺顺序,优化了注入工艺的参数,以在“鳍”的底部形成适当的掺杂PN结,但它同样也是充满了挑战性。

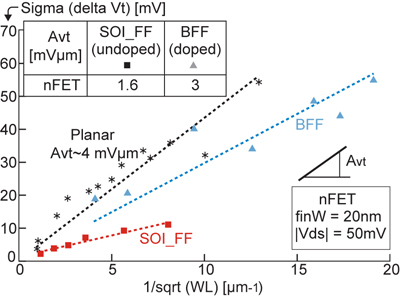

即使是在最佳条件下,离子注入工艺也会产生掺杂梯度,由于在“鳍”体的内部存在注入掺杂的梯度分布,使得要在“鳍”底形成足够剂量的注入掺杂成为一件非常困难的事情。要使SOI和体硅FinFET器件可以达到相当的漏电性能,体硅FinFET中掺杂剂量的随机涨落都将影响到晶体管的性能(图3)。SOI器件由于不需要进行PN结隔离的离子注入,就不会有这种效应。

图3.SOIFinFET、体硅FinFET和平面晶体管的性能比较[2]。

PN结隔离和SOI氧化埋层隔离在结构的不同还会影响到器件的寄生电容。由于设计结构不同,所有的FinFET器件都比类似的平面晶体管更容易产生寄生效应[3]。氧化埋层的存在有利于减少SOI器件的寄生电容,而PN结隔离的体硅器件却需要接受“PN结”带来的额外电容。然而,当“鳍”的高度增加时器件的总电容会增大,使得PN结电容的贡献将变成次要的因素。如果“鳍”高度大于40~50nm,PN结电容的存在将只会使环形振荡器的性能影响5%~6%。

减少差异性

虽然可以通过对其性能的对比来评价不同的候选工艺,但是“最好”的工艺往往由于其由于设计不同而差别很大。高性能的设计可能并不太关注器件的总体成本,而是更为关注器件性能的差异性以及如何来降低它们的差异性。一种低功耗的消费类芯片可能最为关心的是漏电流和功耗问题,但也可能对成本非常敏感。与其试图解决所有这些问题,还不如将我们的分析聚焦于在简化了的通用工艺的差异性和成本问题上。

从器件成本和差异性的观点来看,我们的模型可以被看作是最好的案例:它只考虑一个具有单一阈值电压的数字电路单元。假设只考虑一个“鳍”的节距,这是一个可能的假定,就像制造商可能会通过在一个给定的器件上增加“鳍”的数量来调整晶体管的线度一样。采用单个“鳍”节距可以简化光刻和蚀刻工艺,这是一个重要的简化考虑,因为上述两种工艺本身都很可能在22nm技术节点时面临着挑战。

更实际的器件可能需要增加成本和增加工艺的步骤数。添加阈值电压调整就需要增加新的离子注入掩模,而添加金属层需要增加更多的金属层淀积、图形光刻以及抛光等工艺步骤。我们希望读者能够在我们所提供的框架内来评价它们本身的工艺。

为了对器件差异性进行分析,我们假设SOI和体硅的FinFET器件都采用类似的工艺设备集合,例如,我们认为SOI沟槽刻蚀并不比体硅相应的工艺能达到更严格的容差,我们还假设两种工艺设备集合在随后都能进行相同的工艺改进。

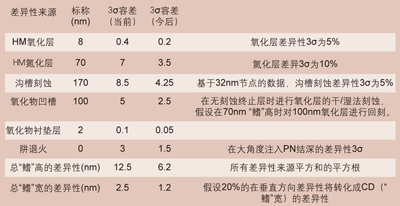

然而,体硅FinFET器件所需要增加的额外工艺步骤切实增加了其差异性。在SOI工艺流程中(表1),最主要的差异性来源是基片硅层本身(它决定了“鳍”的高度)、“鳍”刻蚀的垂直性以及其边墙质量。体硅FinFET器件(表2)也同样会受到“鳍”刻蚀差异性的影响,而且在实际上,由于它还需要额外的氧化物隔离,这意味着在具有更高的深宽比情况下“鳍”必须能保持好它的垂直轮廓。此外,与SOI的氧化埋层可作为刻蚀终止层相比,体硅FinFET不管是“鳍”的刻蚀还是凹槽氧化层的刻蚀都没有刻蚀终止层,而只能依靠时间来控制刻蚀过程,成为控制工艺差异性的一个弱点,同时它还存在微负载效应。最后需要强调的是,如同我们前面所讨论的一样,对PN结隔离注入的控制也将是非常困难的。

表1.产生SOIFinFET器件差异性的来源。

表2.体硅PN结隔离FinFET器件差异性的来源。

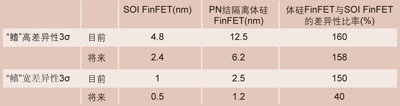

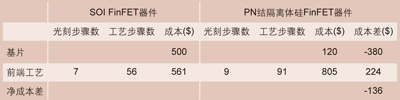

体硅FinFET器件工艺步骤不但可能存在着更大的差异性,而且在工艺步骤数量上也超过SOI器件。如表3所示,在我们的模型中,SOI工艺需要56个工艺步骤,而使用PN结隔离的体硅工艺则需要91个工艺步骤,还包括增加了两个额外的掩模层。即使所有的工艺步骤差异性都相同,体硅FinFET器件也将面临更多的工艺差异性。在我们的模型中,我们预测体硅FinFET器件工艺的差异性将会达到SOI器件的140%~160%(表4)。

表4.SOIFinFET器件和PN结隔离体硅FinFET器件的差异性比较。

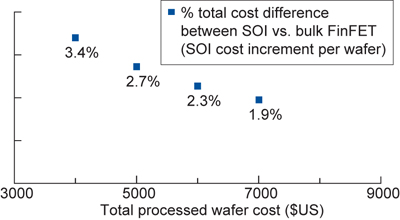

体硅FinFET器件所需增加的额外工艺步骤同样会增加相应的工艺成本(表3)。由于在SOI晶圆在大批量生产使用数量的不断增长,我们预计到2012年,SOI晶圆的成本将降低至每片$500。即使SOI晶圆的成本依然会比体硅晶圆高,但随着单个晶圆总制作成本的提高,晶圆材料成本对整个制作成本的贡献量将会降低。即使是对于我们的模型而言,采用SOIFinFET器件每个晶圆的总净成本也只增加了$136。对于更为实际的工艺流程,我们预计体硅和SOI在成本上的差别将会缩小到我们本项研究的误差范围之内(图4)。

表3.SOIFinFET和PN结隔离体硅FinFET器件的成本对比,模型假设参见文中。

图4.SOI和体硅FinFET器件的总成本之差(相对于总的晶圆制作成本)。

结论

本文评价了在体硅晶圆上采用PN结隔离方法制备的FinFET器件和SOI晶圆上制备的FinFET在器件的性能、差异性和成本上的不同。我们的分析表明,在所有的实际应用中,体硅和SOI晶圆具有类似的性能和成本;但是,由于体硅FinFET器件具有更大的工艺差异性而使得制造变得更具挑战性。体硅晶圆加工的高差异性使其最终产品的性能变得不可预测。我们发现,两种工艺方案具有类似的直流DC和交流AC特性。与SOIFinFET相比,PN结隔离FinFET器件性能将会受到寄生电容增大5%~6%得影响。

与此相反,对工艺差异性的比较表明,SOIFinFET器件可能具有更好的匹配特性。在SOI工艺中,“鳍”的高度和宽度可能更加容易控制,而体硅工艺则在制造和工艺控制方面面临着更为严峻的挑战。

在22nm技术节点阶段,对提高器件密度的期望使得FinFET器件开始具有比平面技术更为实在的优势。

首先,接触栅极的节距必须按比例缩小到小于约束栅constraininggate的长度,也就是要小于所有高性能晶体管的沟道长度。FinFET器件本身所具有的短沟道性能优势将可以进行上述的按比例缩小,而不会产生在平面晶体管中由于需要进行大面积沟道掺杂所引起的有害效应。

同时,对SRAM位单元的期望已开始规定对每个独立晶体管在差异性上的要求。未掺杂的体硅FinFET器件,正如大多数重点研究所关注的,是需要消除注入掺杂浓度的随机波动(RDF)对器件差异性的影响,对于低工作电压的高性能SRAM位单元来说,去除这种RDF可能是必需的。

SOIFinFET由于增加了基片的成本,使其总的器件成本有所增加。但在大批量生产中,这种基片成本的增量将在很大程度上能抵消由于体硅器件复杂工艺造成的成本增量。

14纳米FinFET工艺成争夺焦点全球代工战拉开帷幕

14nmFinFET工艺优势多多,相比业界的20nm工艺,14nmFinFET工艺可提升20%的速度,降低35%的功耗,晶体管密度提升15%。

全球代工的战火再起,由之前的28nm向16nm/14nmFinFET工艺延伸。28nm制程可以认为是半导体业的拐点。因为一直以来依尺寸缩小所推动产业进步至此发生巨大的变化,通常每两年前进一个工艺节点,减少制造成本约50%的节奏,到了28nm以下开始减缓,部分情况下成本反而会有所上升。反映到产业层面,企业向更小尺寸迈进的动力己不如从前。许多顶级的IDM大厂,从28nm开始执行轻资产策略(fablite),拥抱代工。这导致全球代工厂如日中天。

特别是日前三星继英特尔之后宣布14nm将量产,使得代工争夺战中16nm/14nm订单成为新的焦点。全球代工第一阵营中,原先有台积电、联电及格罗方德(Globalfoundries),现在IDM超级大厂三星及英特尔也加入代工行列,导致代工第一阵营中的争斗形势呈现复杂化。

AMD获14nmFinFET工艺能否站起

全球第二大晶圆代工厂GLOBALFOUNDRIES(以下简称GF)是从AMD分出去的,而且也是AMD最重要的合作伙伴之一,虽然傍上的中东土豪很有钱,但是土豪们并不懂技术,GF公司独立初期在28nm工艺上进展不顺,AMD第一代LlanoAPU就深受其害,之前签订的长期供货协议也让AMD宁愿选择赔钱也要脱离泥坑,这事直到现在都在影响AMD的业绩。不过现在AMD有点盼头了,GF日前宣布跟三星电子达成了14nmFinFET工艺授权协议,新一代工艺应该会稳定下来了。

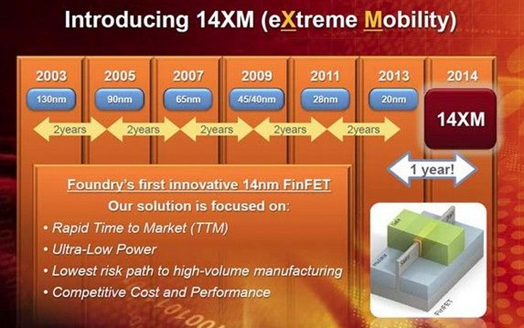

GF之前推过14nm-XM工艺

三星电子、GF以及IBM都是通用开放联盟(CommonPlatformAlliance)的成员,三者共同投资半导体工艺研发,技术共享,此前就有消息称他们将在14nm节点上启用FinFET工艺,Intel的说法是3D晶体管,他们在22nm节点上就已经使用了这种工艺。

双方签署的是多年授权协议,目前14nmFinFET工艺的PDK(processdesignkits,处理器设计套件)已经有了,客户已经可以使用新模型、设计工具及技术文档开始设计工作了,预计今年底会正式量产14nm-FinFET工艺

GF与三星的声明说是二者合作,实际上是三星授权14nmFinFET工艺给GF公司。GF之前也曾推出过14nm-XM工艺,这种工艺将使用FinFET工艺,但是会混合20nm工艺的部分优点,预计在2014年量产。不过回头看看GF两年的工艺进展,别说14nm-XM工艺了,20nm工艺也没见他们规模量产,目前只有TSMC的20nm工艺才正式量产。

所以GF与三星的14nmFinFET授权协议很可能意味着GF自家的14nm-XM工艺玩完了,因为三星的14nmFinFET工艺优点更多,三星开发14nmFinFET工艺的时间更长,经验更丰富。

第二个受影响的则是AMD,所以AMD全球副总LisaSu也在声明中表态了,她表示GF、三星的合作给了AMD一个增强他们技术IP的机会,双方的先进工艺将为AMD新一代产品奠定基础。

最后,三星、GF的合作也让之前GF与苹果的暧昧关系更有根据了,此前就有传闻称GlobalFoundries也可能加入苹果代工阵营,还有三星的工程师帮助GF建厂。苹果的去三星化人尽皆知,今年的A系处理器已经基本确定会有TSMC的参与,未来也可能会有GF的份,如果他们的制程工艺能够稳定下来。

苹果与高通订单成风向标

三星与格罗方德联盟可能提前进入14nm量产,高通与苹果的订单会成争夺焦点。

全球代工的客户70%来自fabless,而依目前的态势,其中高通与苹果两家大户的订单成为争夺焦点。反映出半导体业的推动力正由PC转向移动终端,包括手机及平板电脑等,整个产业供应链发生大的改变。

高通依靠向全球智能手机提供芯片及专利授权,2013年销售额己达248亿美元,其中1/3来自授权费用。据Ddaily2014年5月的数据,在全球移动处理器市场中,高通市占率分别为:2011年48.7%、2012年42.9%、2013年53.6%。苹果相应分别为14.4%、15.90%和15.70%。这是因为苹果仅在手机及平板电脑中采用自己设计的处理器芯片,Mac计算机中仍采用英特尔芯片。

高通在移动处理器行业拥有无可争议的霸主地位,虽然说目前已经有其他fabless厂商对于高通形成压力,但其优势依旧非常明显,各大品牌手机的旗舰机几乎都清一色地使用了高通芯片。目前高通的高端芯片骁龙805,64位8核,采用20nm工艺。

苹果手中也握有大订单,之前由三星代工,近期它自己设计的20nm制程A8芯片已部分移至台积电加工。显然台积电是想继续扩大战果,争取2015年它的16nm生产线上可为苹果的A9处理器代工。但是情况是错综复杂的,其中既有竞争关系,也有技术方面的问题。谁都清楚,2015年三星与格罗方德联盟可能提前进入14nm量产,相比台积电的16nm制程具有优势。连张忠谋也坦承这一步台积电可能会落后,所以把希望寄托在2016年的10nm制程决战上。但是,三星与格罗方德联盟有可能受到产能不足困绕,为未来竞争平添了变数。而目前台积电已经拥有20nm制程产能达7万片/月。不管如何,高通与苹果的订单会成为争夺焦点,但是苹果的原则是不把鸡蛋放在同一个篮子里。

代工战场谁能胜出?

台积电在代工中独霸的态势,尽管近期内无法动摇它,但是会受到侵蚀。

代工业的成长不可能一蹴而成,其中台积电的老大地位不可动摇。尤其是2009年张忠谋第二次执掌公司以来,采用令人胆寒的积极投资扩张策略,在2010年~2013年期间总投资达300多亿美元,使得先进制程技术不断推进,再次稳固了代工龙头地位,并取得十分喜人的结果。

2013年台积电总产能约月产130万片(8英寸计),其中28nm产能为月产13万片(12英寸计),全球市占率按销售额计达80%。而且它的28nm爬坡速度非常快,2011年第四季度它的28nm刚刚启步,季销售额才1.5亿美元,至2012年年底已经占年销售额170亿美元的24%,达40.8亿美元,2013年年底占近200亿美元销售额的37%,达到65亿美元。

以每月6万片晶圆的产能来计算,台积电20nm制程晶圆的平均价格估计在2014年第四季度达到每片6000美元,与28nm晶圆平均价格(约4500美元~5000美元)相较有很大的提升。而估计其16nm/14nm的FinFET晶圆的生产成本约为每片4000美元,加上毛利率约45%,销售价格则为每片7270美元。如果台积电对于20nm制程的预测准确,从整体上看它的20nm制程的市占率,将会在2014年第四季度时达到全球的95%。

由此可以看出台积电代工老大地位不可动摇的原因:一是成品率高达90%,对手们可能约70%;二是拥有向客户提供支持的约6300项IP专利,业界戏称如有个“图书馆”一样;三是产能迅速到位,如28nm的产能达月产13万片,是格罗方德的3倍。

台积电在代工中独霸的态势,尽管近期内无法动摇它,但是一定会受到侵蚀,也即它不太可能维持住48%以上的高毛利率。其中的争夺既有16nm/14nm也有28nm代工。28nm目前仍是主战场,因为这一块的全球市场规模约有80亿美元~100亿美元。三星与格罗方德联盟的优势在于提出了FDSOI的28nm新工艺路线,对于要求更低功耗的芯片具有吸引力。另外,它们的代工价格一定会低于台积电。

至于联电与中芯国际的28nm,尽管它们都声称马上能准备好,但受限于产能,以及技术上的爬坡时间,想要获得大的突破,尚需时间。

另外,不可否认英特尔是个潜在对手。因为从工艺制程的技术水平以及研发投入上看,它肯定都是全球最领先的。但是,英特尔欲从IDM模式转向代工不是一件容易的事。一方面是把大量的产能转向代工,英特尔从思想上尚未下最后的决心,英特尔处理器的平均毛利率高达68%,代工厂毛利率可无法有那么高。另一方面,它缺乏代工所需配套的IP,这不是短期内就能准备就绪的。所以近期英特尔的高管透露了其意图,仅是通过代工来维持少数几个高利润率的客户。

产业格局前景难料

在16nm/14nm区段,台积电、三星、英特尔等各家,都不具备必胜把握。

与28nm代工产业不同,未来全球16nm/14nm及以下的代工格局前景难料。因为目前全球半导体业的现状是这样的:从技术上每两年前进一个工艺节点,理论值是2013年14nm及2015年10nm,可实际上英特尔的14nm量产推迟到了2014年第四季度,相比正常情况延长了两个季度。台积电更是灵巧,声言2014年是20nm量产及2015年才是16nm量产的时间点。三星电子推出先进代工制程14nmFinFET的应用处理器(AP)试制品,将先提供给高通、苹果、超微(AMD)等主要客户,但是目前它们的产能不足,三星才月产1万~1.5万片,格罗方德才3.5万片。两者加总才月产5万片。

更关键的是,目前10nm工艺制程都是处于研发阶段,包括英特尔、台积电及三星在内,离真正量产尚有距离,其中的变数还很多。最乐观的预测,10nm制程也要到2016年才能量产。另外,10nm制程之后,究竟如何往下走,尚不十分清楚,其中包括EUV何时准备好难以预言,10nm时193nm光刻工艺的成本与栅极材料的替代品的工艺等尚未完全就位。

按Gartner的观点,从近期来看,在1~2年内FinFET的量产,全球代工的产能需求不会超过月产5万片。而到2018年前也不会有大于月产25万片的市场需求。而这样的市场需求有两家大的代工厂已经足够,所以现在众多的一线代工厂纷纷进入FinFET工艺,未来一定会发现有人失声。

按PacificCrestSecurities的分析师的观点,从投资规模计,16nm/14nmFinFET技术投资1万片产能要12.7亿美元的投资,再增加2万片需25亿美元的投资。

还有一个不能言透的问题,技术方面谁能真正过关,即成品率能同步吗?据目前的态势,无论台积电的20nm量产还是英特尔的14nm量产,都出现了推迟的现象,都有成品率的问题存在其中。所以,未来究竟谁的技术真正过关还需观察。

客观地分析,英特尔占有一定优势。因为它从2011年的22nm节点就开始采用FinFET技术,至今已经是第二代了,经验相对多一些。否则也不可能发生原是台积电老客户的Altera,突然转向拥抱英特尔的14nm芯片代工的情况。还有,近期松下电子也下单给英特尔。足以证明其在技术方面可能高出一头。但是也不可否认,英特尔在代工方面尚有许多问题。所以在16nm/14nm这一区段,无论台积电、三星与格罗方德联盟,还是英特尔,哪家都不具备必胜的把握。

高通拟转单三星、苹果也蠢蠢欲动

外传高通(Qualcomm)Snapdragon810处理器有过热问题,先前小摩说对台积电(2330)影响有限。然而Maybank看法不同,认为高通未来晶圆代工订单将由三星电子(SamsungElectronics)和台积电分食,台积电不再独享大单。

Barronˋs11日报导,Maybank分析师WarrenLau认为,高通在高阶64位元晶片生产研发上,落后苹果和三星。采台积电20奈米制程的Snapdragon810可能赶不上三星GalaxyS6开卖时程,不少中国和外国厂商也因此打算改用联发科28奈米的MT6795晶片。

高通为了追上对手,可能会迅速转向14/16奈米,当前的20奈米晶片将为过渡期产品,未来可能把14奈米FinFET订单交给三星、16奈米FinFET订单交给台积电,不像之前由台积电独揽订单。2013年高通占台积电营收17%,估计2014年比重增至近20%。

不仅如此,三星和英特尔(Intel)晶片终于赶上台积电大客户高通,三星旗舰机可能不再高度仰赖高通,改用自制晶片取而代之。三星S6开卖初期,若因高通出货不及,改用自制晶片,台积电营收可能会损失台币90亿元,占台积电第1季营收的5%。

TomˋsHardware7日报导,高通产品管理副总TimLeland澄清,新技术问市总会遇上工程挑战,但是没有出现会延迟出货的重大技术问题。LGGFlex2预计1月底出货,外传搭载Snapdragon810,届时就可知道延误是否为谣传。

Barron8日报导,JP摩根分析师GokulHariharan、JJPark与RahulChadha发表研究报告指出,高通最新64位元Snapdragon615、Snapdragon810处理器的确有过热的疑虑,这些问题在去(2014)年12月就开始浮出台面,尤其是对用于高阶机种的Snapdragon810而言,且问题至今尚未解决。

为了修正Snapdragon810的问题,高通可能得重新设计数个金属层,预估会让进度延后3个月。这意味着,Snapdragon810最快要到2015年第2季中旬才能量产。三星电子(SamsungElectronics)预定2月发表的次代旗舰机「GalaxyS6」当中,很可能会有超过90%的出货量改用自制的Exynos应用处理器和数据机,与过去几年逾7成出货量使用Snapdragon的状况大相径庭。

另外,苹果A9处理器订单花落谁家,外资众说纷纭。根据BernsteinResearch的说法,三星由于FinFET制程技术较为先进,因此很有机会取得次世代iPhone的处理器订单,相较之下台积电则有望取得较大尺寸的iPad以及低阶iPhone的处理器代工业务。

综上所述,未来全球16nm/14nm及以下的代工格局前景难料。

22nm乱世之最后悬念:多角度看Finfet等四种技术优劣对比

2011-07-2021:08:02次阅读次推荐稿源:条评论

在向22/20nm节点制程攀登的过程中,半导体技术研发者们似乎纷纷准备在这一节点推出新形态的晶体管结构技术。这方面做得比较出彩的有Intel,他们不久前正式公布将在22nm制程节点启用三栅晶体管技术,并因此而博得了许多人的关注。不过,其它公司、机构的研发人员同时也在不断推进三栅晶体管的同类-Finfet技术的开发工作。与之形成鲜明对比的是,包括ARM,以及有浓厚AMD背景的Globalfoundries在内的欧洲半导体技术组织,则在大力推广全耗尽型SOI,即FDSOI技术。另外,最近一家名不见经传的新兴公司Suvolta则联合富士通公司推出了第三种晶体管技术方案。当然,最后我们也不能忘记台积电已经表态会在20nm节点继续使用常规的平面型晶体管技术。

虽然说有关的话题对器件设计者而言很有吸引力,而对芯片设计者来说则表面上看似乎并不与其本职工作有什么必要的联系。但大家不要忘记,晶体管的设计技术会对许多下游因素,包括从功能单元的设计到物理层设计,乃至到逻辑层设计过程造成影响,并最终影响到芯片的功耗和时序,而这些因素则是芯片设计者们必须关注的重要项目。

为什么要对晶体管结构技术进行变革?

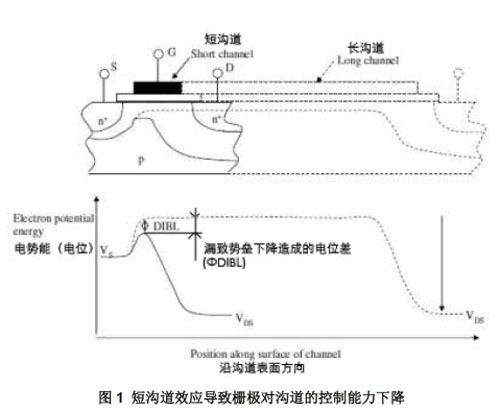

制程工程师们为什么要变革现有的晶体管结构技术呢?简单来说,原因在于所谓的短沟道效应(SCE:short-channeleffects).为了跟上摩尔定律的脚步,人们不得不不断缩短MOSFET场效应管沟道的长度。这样做有可以增加芯片的管芯密度,增加MOSFET的开关速度等等好处。然而,沟道长度的缩短却会带来许多其它的负面效应。总得来看,造成这些负面效应的原因多数可以总结成这样一句话:随着器件沟道长度的缩短,漏极与源极的距离也随之缩短,这样一来栅极对沟道的控制能力变差,栅极电压夹断(pinchoff)沟道的难度也越来越大(如图1),如此便使亚阀值漏电(Subthrehholdleakage)现象更容易发生。

其实,人们早在90nm节点便已经开始向短沟道效应宣战。而后来大行其道的HKMG技术推出的目的之一也正是为了在增强栅极对沟道电流的控制能力的前提下,尽量地减小栅极的漏电流。不过到22nm节点,短沟道效应愈发严重,仅仅依靠HKMG和过去的技术,而不对传统平面型晶体管的结构作出变动,已经无法满足要求,无法在保证器件性能达标的同时,对器件的漏电进行足够的限制。用一位专家的话说:“HKMG解决了栅极漏电的问题,现在我们需要处理的则是沟道漏电的问题。”

继续走平面型晶体管的老路吗?

不过并不是所有的人都认为传统的平面型晶体管已经走到了穷途末路。台积电便是其中的一员,今年2月份,他们曾经表示将在20nm制程节点继续使用平面型晶体管结构,而Globalfoundries则也有类似的计划。关于这种立场的对错,业内的争论颇多。设计者们对短沟道效应及其危害是非常熟悉的。在20nm节点,短沟道效应造成的漏电和门限电压变差现象也许会比28nm节点更加严重,不过设计者们也有对付这种问题的办法,比如在设计时采取严格的电源管理技术,使用容差电路,统计时序分析法等等。而当所有这些问题出现时,作为芯片代工方的台积电或Globalfoundries必然会要求他们的客户,如FPGA厂商,网络芯片厂商,ARM等向其芯片中加入这些弥补性的电路设计。

对此持怀疑论的芯片厂商并不在少数。比如Novellus公司的副总裁GirishDixit就表示:“台积电宣称他们会在20nm节点制程使用替换型金属栅技术(即常说的GatelastHKMG)+传统平面型晶体管的技术组合,不过这种计划恐怕会发生一些变故。虽然HKMG技术具备控制漏电的能力,但是由于仍然采用传统的平面型晶体管技术,因此其Ion/Ioff性能难免相对低下。”如果台积电的客户发现这些采用传统平面型晶体管技术制作的芯片在效能方面处于不利的地位,那么他们完全有可能逼迫台积电提前在20nm节点启用Finfet技术。在移动设备用芯片市场,这种情况是最有可能发生的,因为以ARM为首的芯片设计合作伙伴们需要面对的是采用三栅技术的22nm制程Intel的同类型Atom产品。

Finfet的崛起:

十多年前,技术人员便已经开始研究与Finfet以及其它与下一代晶体管结构技术有关的技术,不过今年5月份,Intel将这项技术从阳春白雪的研究室搬到了面向市场和公众的大舞台上。虽然他们让三栅技术走向前台的动机未必纯洁--从很大程度上看是为了在移动设备芯片市场向ARM阵营施压,而不是为了改善电路设计,减小半导体器件信噪比,推动半导体技术向前发展等冠冕堂皇的目的。

从本质上说,Intel口中所谓前无古人的三栅技术,在业内专家的眼里看来其实就是一种彻头彻尾的Finfet技术,其与人们已经研究了十多年的Finfet并没有本质的区别。一位专家表示:“其实业内所有的厂商都在开发Finfet技术,两者唯一的区别就是Intel的那一套鼓动人心的说辞。”

总的来看,其实包括Finfet在内的所有下一代晶体管结构技术,其革新的思路都是基于全耗尽型沟道的理念。简单地说,全耗尽沟道技术令栅极对沟道处形成电场的控制能力大为增强,在栅极的控制下,当器件需要处于关闭状态下时,沟道中所有的载流子均会被耗尽,这样沟道将不再具备任何导电能力,也就意味着晶体管漏源极导电通路的彻底关闭。

那么全耗尽沟道技术又是如何做到这一点的呢?在传统的部分耗尽型平面晶体管中,由于漏源极与硅衬底形成反偏的PN结结构,因此其周围有耗尽层结构存在,加上沟道的深度有限,这样沟道处的电场就会受到这些因素的干扰而偏离理想的状态。要解决这个问题,可以采用令沟道区域的硅膜厚度极薄,薄到与沟道的深度相同,并且拉大沟道与漏极反偏结的距离的方法,来构造全耗尽型的沟道区。

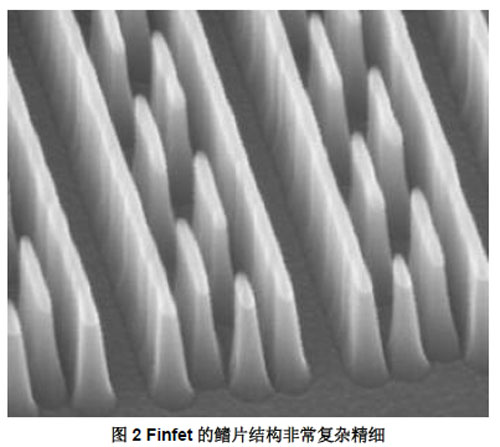

新一代晶体管技术:Finfet

Finfet的解决方法是另沟道从硅衬底表面竖起,形成垂直型的沟道结构(又被人们形象地称为Fin-鳍片),然后再在鳍片表面构造栅极。Finfet的鳍片厚度极薄(如图2),且其凸出的三个面均为受控面,受到栅极的控制。这样,栅极就可以较为容易的在沟道区构造出全耗尽结构,彻底切断沟道的导电通路。

Finfet器件实现了从130nm节点人们便一直梦寐以求的极高伏安性能。但是这种技术同时也带来了新的问题。如何制造符合要求的Finfet器件便是难题之一。应用材料公司的高管KlausSchuegraf为此警告称:“如何制作Finfet的鳍片结构,以及如何在后续的制程工序中保持鳍片的完整性是一项非常困难的任务。你必须解决如何完成高深宽比结构的蚀刻,如何将杂质均匀地掺杂到三维表面,如何在鳍片上生成复杂多层结构的栅极,并且保证栅极的形状与鳍片完全贴合等等问题。要解决这些问题,就必须对材料,生产设备进行改进。虽然用于制造Finfet器件的掩膜板数量并不会增加很多,但是制造工序的数量则一定会增加。”

Finfet给芯片设计者带来的新问题:

不仅如此,芯片的设计者们也会遇到一些新问题。在Finfet设计的电路中,鳍片的宽度将会是电路中最小的制程尺寸参数。在目前的光刻技术条件下,为了形成鳍片结构,就必须使用双重成像技术(具体点说,很可能是采用SADP自对准双重成像工艺)。而据Schuegraf介绍,双重成像技术的实现要求芯片设计者在设计芯片时采用非常严格的设计准则。Intel器件研发部门的经理MikeMayberry则称:“大部分设计准则都是为了改善对光刻工艺的兼容性而设置的。一旦你学会如何设计22nm节点电路Layout,那么在面对三栅时你只需要注意留心少量专设的设计准则即可。”

对电路设计者而言,Finfet技术也会带来一些变化。其中最明显的变化之一是,在试图增大管子的驱动能力时,过去简单增加线路宽度的方法在三栅中已不再适用,Finfet器件中鳍片的高度和宽度必须保持不变,而以增加鳍片数量的方法,来增加器件的驱动能力。这是由于芯片中所有鳍片的高度尺寸都必须由同一次抛光工序来进行定义,无法对个别鳍片的高度进行拔高或降低处理。

而鳍片的宽度尺寸也有类似的情形。Dixit介绍说,鳍宽无法自由调节的原因并不仅是由于光刻技术方面的限制,鳍宽的增加还会影响到MOSFET门限电压的变化.如果你试图增加鳍片的宽度来增加器件的驱动电流,那么器件的门限电压也会发生改变。

反过来看,这也意味着在Finfet的制造过程中必须保证鳍片的宽度和高度必须保持一致,否则便会对器件的门限电压等性能参数造成影响,导致电路中各个晶体管的性能参数彼此差异过大。

要增加器件的驱动能力,你只能采用增加并联的鳍片数量的方法来达到目的。而由于每个鳍片传输的电流是一个固定值,这也意味着器件驱动能力只能以这一定值为单位进行增减,这对电路设计者,尤其是一些定制型模拟电路的设计者而言显然是一个令人不快的限制。不过Intel看起来似乎并没有因此而感到担心,他们表示:“我们已经针对开关型和放大器型两种应用,对我们的三栅电路进行了调整。因此我们认为只有在极少数的情况下,才需要对电路设计进行调整。”

相比之下,其它的业内专家在这方面的态度则显得悲观许多,比如IMEC组织的执行副总裁LudoDeferm就表示说:“要得到较高的驱动电流,你必须将多个鳍片并联在一起,这就需要在多个Finfet之间设置互联线路。但是在高频条件下工作时,由互连线造成的电路电阻增加则会影响到电路的性能。”

FDSOI:通向全耗尽型沟道的另一条路

面对Finfet带来的新问题,FDSOI的支持者们找到了机会,他们宣称FDSOI可以在达到同样性能水平的条件下解决Finfet的这些问题。从外表上看,FDSOI晶体管与传统的部分耗尽式平面型晶体管(PDSOI)并没有太大的区别,前者仍然采用平面型的结构,不过FDSOI中最顶层,即位于埋入式氧化层结构顶部的硅膜厚度相比传统的PDSOI要减薄了许多。FDSOI拥有许多显见的优势,比如器件的结构形式相比传统平面型晶体管基本变化不大,消除了PDSOI因浮体效应(Floatingbody)所导致的记忆效应(电荷会在浮体结构中累积,导致浮体电位的增加,从而导致门限电压的变化)。另外,据法国半导体厂商Leti的高管OlivierFaynot宣称,FDSOI相比对手的技术而言,晶体管性能可以提升60%,或者器件的功耗可以降低50%。

也许FDSOI的优点中最明显的就是门限电压的控制方面。由于FDSOI采用的是无杂质掺杂的纯硅沟道设计方案,因此电路中各个MOSFET其沟道的杂质掺杂浓度不会存在相互的变差,而沟道杂质掺杂浓度的变差,则会导致MOSFET器件门限电压的变差。而这个问题在Finfet和传统平面型晶体管器件中则同样存在。更进一步看,当需要采取多门限电压设计时,Finfet和传统平面型晶体管必须通过改变沟道杂质掺杂浓度的方式来改变器件的门限电压,而在常规平面型晶体管中,要实现这种调节的难度甚大,对Finfet而言,则目前几乎无法实现这种调节。而在FDSOI中,则可以通过向埋入式氧化层底部的硅衬底施加电压,来起到动态地改变门限电压的目的。

当然,FDSOI也不是完美无暇,这项技术主要有三个缺点。首先,FDSOI晶圆的成本要比传统的PDSOI胡体硅晶圆更高。不过按照上周一家市调公司ICKnowledge公布的所谓成本分析报告称,由于FDSOI器件具备多门限电压可控的优势,因此采用FDSOI技术制作的22/20nm器件的总制作成本实际上比传统平面型产品或Finfet并没有太大差别。

第二个缺点在于晶圆制造方面的技术风险。目前法国Soitec公司是FDSOI晶圆的唯一生产商,而FDSOI晶圆的制作需要保证晶圆中氧化层淀积,晶圆切割,晶圆抛光等各个工序的加工精度都能够达到原子级别。目前Soitec供应的FDSOI晶圆其顶部硅层厚度为12nm,埋入式氧化层的厚度尺寸则同样极薄。

第三个缺点--其实准确点说应该是弱势,便是来自于一部分企业高管的惰性。有一些企业的决策者总是对和SOI有沾边的技术不理不睬。在这方面,AMD及其子女Globalfoundries,IBM以及意法半导体等公司则为这些惰性十足的企业高管树立了榜样,他们在22nm节点很有可能将启用FDSOI技术。特别是Globalfoundries,他们过去在SOI有关产品的推广上并不是非常积极,不过现在当面对来自Finfet阵营的Intel和台积电的挑战时,他们很有可能要拿起FDSOI作为对抗的武器。而且一部分过去已经采纳过PDSOI技术的芯片设计厂商,比如Broadcom等也有可能会选择追随FDSOI。不过据一位熟知内情的人士表示:“除此之外,FDSOI恐怕不会引起更多人的注意。”

玩非主流的SuVolta和富士通等:

除了FDSOI和Finfet之外,还有第三种新技术可以同样形成全耗尽型沟道。不久前SuVolta公司宣布推出了一种新的MOSFET结构,这种MOSFET中,使用淀积工艺在传统体硅平面型MOSFET的沟道下方埋入了一种PN结结构,当这种PN结反偏时,会在沟道的下方形成耗尽区,如此就可以起到与FDSOI中沟道下方埋入式氧化物同样的效用,同时又可以减薄沟道的厚度,这样在栅极的控制下,沟道便可处于全耗尽的工作状态。

SuVolta的这种技术看起来挺引人注目,不过有关这项技术的细节,除了与这家公司有密切合作关系的少数几家公司如富士通之外,外界对其所知甚少。另一方面,SuVolta这种技术的效能也还没有经过独立机构的验证。不管怎么样,也许这种技术会受到类似富士通的一些小型公司的青睐,这些小公司手头的资金还不够充裕,无法加入Finfet的战团,同时也付不起加入FDSOI阵营所需的启动金。

总结:

最后,我们来总结一下实际的芯片制造商在这三种选择中会如何抉择。

1-台积电20nm节点看起来会继续走常规平面型晶体管的老路--至少在制程推出的初期会是这样。不过台积电很可能会很快在16nm节点制程到来之前,对其20nm技术进行调整,并推出面向移动设备用芯片应用的Finfet制程产品。

2-Intel方面已经表态会坚持走Finfet路线;

3-IBM以及Globalfoundries和意法半导体公司很可能会在推出的芯片产品中全部或部分地采用FDSOI技术;

4-富士通等小公司则会继续与SuVolta合作应用其独特的技术。

其它的厂商会选择站在哪一边,无疑将根据其客户的需求,以及采用Finfet,FDSOI等新技术的先锋厂商产品的实际表现对比而定。不过,联想到目前各家厂商在28nm制程中所遇到的种种问题,这几种新制程技术在应用的初期恐怕都不太可能会有一帆风顺的好运气。

传三星已开始制造14nmFinFET工艺处理器

腾讯数码[微博]蝉蝉2014年12月16日07:38

[摘要]三星半导体业务副总裁表示,已经开始生产14nmFinFET工艺处理器,外界普遍认为客户应该是苹果或高通,也有可能是AMD。

腾讯数码讯(编译:蝉蝉)继上月底三星宣布自家的Exynos处理器已经实现14nmFinFET(FinField-EffectTransistor,鳍式场效晶体管)工艺量产之后,近日三星半导体业务副总裁KimKi-nam表示,已经开始14nmFinFET工艺处理器的生产合约,但是他并未透露具体的合约客户以及详细的产品细节。

尽管如此,外界普遍认为此次三星14nmFinFET工艺处理器的客户应该是苹果或者高通,也有可能是AMD。如果是苹果的话,那么不是AppleWatch的S1处理器就是下一代iPhone的A9处理器,不过现在就开始量产A9处理器似乎有点早了,难道苹果打算将iPhone的更新周期缩短为半年?另外,高通在今年早些时候也对三星的14nmFinFET工艺表现出了浓厚的兴趣,但到目前为止高通并没有公布14nm处理器计划,而目前高通最先进的骁龙810处理器采用的是20nm工艺。

根据之前的报道,三星在今年年初就展示了14nmFinFET工艺处理原型,并且表示其14nmFinFET工艺相比于台积电的20nm工艺,在性能提高20%的同时,功耗和占用面积分别降低了35%和15%,而三星14nmFinFET工艺的最大竞争对手应该是台积电的16nm工艺。而对于消费者来说,从20nm处理器过渡至14nm处理器应该还需要一段时间,眼下我们应该更期待明年登场的骁龙810和Exynos7410,要知道它们才刚刚用上了20nm制造工艺。

台积电今年年中投产16nmFinFET已无望

http://www.c114.net(2015/1/1610:56)

20nm轻松拿下苹果所有订单,台积电一时间豪情万丈,号称要在2015年初量产16nmFinFET,创下半导体史上两代工艺量产时间最接近的记录,但现实是残酷的。在去年晚些时候,台积电曾宣布16nm工艺已开始试产,将在2015年年中投入量产,已经比最初目标晚了小半年。而来自台湾《电子时报》的消息称,台积电已经将16nm设备安装的时间推迟到2015年下半年了,而原来希望能在上半年完成。这就意味着,台积电16nm量产最快也得今年年底,更大的可能性则是2016年初。

这也同时意味着,苹果的A9已经基本不可能交给台积电,NVIDIA的新显卡也要落空。

与此同时,三星方面传出好消息,14nmFinFET工艺已经克服了此前的问题,良品率大为提升,而且三星一直以低报价死拼台积电。

据了解,高通已经作出决定,终止原计划在台积电进行的16nm芯片试产,转而将订单转交给三星14nm,而苹果A9无奈转回老对头也基本已经定局。

由于GlobalFoundries与三星已经在14nm上达成联盟,AMD作为老东家在显卡上应该不用担心,可以放心地转移,NVIDIA可怎么办呢?去用20nm?

问题是,台积电的20nm也是麻烦缠身。由于苹果iPhone6高峰渐渐过去,20nm产能开始出现过剩,不得不减产20%,同时高通的第一款20nm处理器骁龙810又接连传出存在缺陷、发热量过高问题,大批量出后也可能延迟,最快得三月份——用它的小米Note高配版就是三月底才开卖。

全球代工格局之战风云再起,14纳米FinFET工艺戏诸侯

2015年01月14日

全球代工的战火再起,由之前的28nm向16nm/14nmFinFET工艺延伸。28nm工艺可以认为是半导体业的拐点。因为一直以来依尺寸缩小所推动产业进步至此发生巨大的变化,通常每两年前进一个工艺节点,减少制造成本约50%的节奏,到了28nm以下开始减缓,部分情况下成本反而会有所上升。反映到产业层面,企业向更小尺寸迈进的动力己不如从前。许多顶级的IDM大厂,从28nm开始执行轻资产策略(fablite),拥抱代工。这导致全球代工厂如日中天。

特别是日前三星继英特尔之后宣布14nm将量产,使得代工争夺战中16nm/14nm订单成为新的焦点。全球代工第一阵营中,原先有台积电、联电及格罗方德(Globalfoundries),现在IDM超级大厂三星及英特尔也加入代工行列,导致代工第一阵营中的争斗形势呈现复杂化。

苹果与高通订单成风向标

三星与格罗方德联盟可能提前进入14nm量产,高通与苹果的订单会成争夺焦点。

全球代工的客户70%来自fabless,而依目前的态势,其中高通与苹果两家大户的订单成为争夺焦点。反映出半导体业的推动力正由PC转向移动终端,包括手机及平板电脑等,整个产业供应链发生大的改变。

高通依靠向全球智能手机提供芯片及专利授权,2013年销售额己达248亿美元,其中1/3来自授权费用。据Ddaily2014年5月的数据,在全球移动处理器市场中,高通市占率分别为:2011年48.7%、2012年42.9%、2013年53.6%。苹果相应分别为14.4%、15.90%和15.70%。这是因为苹果仅在手机及平板电脑中采用自己设计的处理器芯片,Mac计算机中仍采用英特尔芯片。

高通在移动处理器行业拥有无可争议的霸主地位,虽然说目前已经有其他fabless厂商对于高通形成压力,但其优势依旧非常明显,各大品牌手机的旗舰机几乎都清一色地使用了高通芯片。目前高通的高端芯片骁龙805,64位8核,采用20nm工艺。

苹果手中也握有大订单,之前由三星代工,近期它自己设计的20nm工艺A8芯片已部分移至台积电加工。显然台积电是想继续扩大战果,争取2015年它的16nm生产线上可为苹果的A9处理器代工。但是情况是错综复杂的,其中既有竞争关系,也有技术方面的问题。谁都清楚,2015年三星与格罗方德联盟可能提前进入14nm量产,相比台积电的16nm工艺具有优势。连张忠谋也坦承这一步台积电可能会落后,所以把希望寄托在2016年的10nm工艺决战上。但是,三星与格罗方德联盟有可能受到产能不足困绕,为未来竞争平添了变数。而目前台积电已经拥有20nm工艺产能达7万片/月。不管如何,高通与苹果的订单会成为争夺焦点,但是苹果的原则是不把鸡蛋放在同一个篮子里。

TSMC终于承认落后了,16nmFinFET工艺2016年才能量产

2015-01-17

TSMC在28nm、20nm节点上进展最快,这两年赚得盆钵满满,三星、GF等对手则选择了跳过20nm直奔14nmFinFET工艺,反倒可以后来居上。TSMC日前在投资者会议上承认,2015年他们的16nm份额会比竞争对手要少,真正量产要到2016年,下下代的10nm预计在2017年推出。

TSMC日前举办了投资者会议,联席CEO刘德音(MarkLiu)在会议上承认,TSMC的16nmFinFET工艺来得有些晚,因此2015年他们在该工艺上的市场份额会比主要竞争对手要少。现在他们正用该工艺为客户认证产品,2016年16nmFinFET工艺就会大规模量产。

此前的传闻都是说TSMC会在今年Q3季度(最快7月份)开始量产16nmFinFET工艺,但现在看来TSMC的进度没有想象中的那么快(放的一手好烟雾弹),昨天传闻的设备暂停安装看起来也是真的了。2015年TSMC只会少量生产16nmFinFET工艺产品,量产还得等到2016年,至少是一年后了。

三星、Globalfoundries都使用了14nmFinFET工艺,后者还是三星提供授权的,三星虽然生产过20nm工艺,但这两家基本上都跳过了20nm节点,真正量产靠的还是14nmFinFET工艺,所以这两家的进展要比TSMC还快。

TSMC的工艺延期会影响很多客户选择,而且三星在代工价格上更优惠,所以苹果的A9处理器据说70%的订单都交给了三星及GF两家。就连一向最优待遇的高通据说也暂停了TSMC的16nmFinFET工艺试产,准备转向三星14nmFinFET工艺。

这些大客户还可以有别的选择,不过国内准备使用TSMC新工艺的客户可能就有些悲剧了,此前TSMC首次试产16nmFinFET选择的伙伴是海思,他们下一代的8核LTE芯片麒麟930传闻就是该工艺生产的,现在不知道如何了,如果真的延期一年多,海思难道要用麒麟920/925再战一年?

16nm工艺进度晚了,TSMC对下一代的10nm工艺又提出新目标了,CEO表示他们的10nm工艺正在开发中,今年底准备进行质量认证,目前正在跟客户合作流片工作,预计量产时间是2017年。

不过有了16nmFinFET工艺的教训,TSMC的客户应该更小心才是,Intel实力如此强劲,10nm工艺量产也要到2017年了。

角逐14纳米FinFET工艺全球代工战火再起

中国电子报、电子信息产业网 作者:莫大康发布时间:2015-01-13

全球代工的战火再起,由之前的28nm向16nm/14nmFinFET工艺延伸。28nm制程可以认为是半导体业的拐点。因为一直以来依尺寸缩小所推动产业进步至此发生巨大的变化,通常每两年前进一个工艺节点,减少制造成本约50%的节奏,到了28nm以下开始减缓,部分情况下成本反而会有所上升。反映到产业层面,企业向更小尺寸迈进的动力己不如从前。许多顶级的IDM大厂,从28nm开始执行轻资产策略(fablite),拥抱代工。这导致全球代工厂如日中天。

特别是日前三星继英特尔之后宣布14nm将量产,使得代工争夺战中16nm/14nm订单成为新的焦点。全球代工第一阵营中,原先有台积电、联电及格罗方德(Globalfoundries),现在IDM超级大厂三星及英特尔也加入代工行列,导致代工第一阵营中的争斗形势呈现复杂化。

苹果与高通订单成风向标

三星与格罗方德联盟可能提前进入14nm量产,高通与苹果的订单会成争夺焦点。

全球代工的客户70%来自fabless,而依目前的态势,其中高通与苹果两家大户的订单成为争夺焦点。反映出半导体业的推动力正由PC转向移动终端,包括手机及平板电脑等,整个产业供应链发生大的改变。

高通依靠向全球智能手机提供芯片及专利授权,2013年销售额己达248亿美元,其中1/3来自授权费用。据Ddaily2014年5月的数据,在全球移动处理器市场中,高通市占率分别为:2011年48.7%、2012年42.9%、2013年53.6%。苹果相应分别为14.4%、15.90%和15.70%。这是因为苹果仅在手机及平板电脑中采用自己设计的处理器芯片,Mac计算机中仍采用英特尔芯片。

高通在移动处理器行业拥有无可争议的霸主地位,虽然说目前已经有其他fabless厂商对于高通形成压力,但其优势依旧非常明显,各大品牌手机的旗舰机几乎都清一色地使用了高通芯片。目前高通的高端芯片骁龙805,64位8核,采用20nm工艺。

苹果手中也握有大订单,之前由三星代工,近期它自己设计的20nm制程A8芯片已部分移至台积电加工。显然台积电是想继续扩大战果,争取2015年它的16nm生产线上可为苹果的A9处理器代工。但是情况是错综复杂的,其中既有竞争关系,也有技术方面的问题。谁都清楚,2015年三星与格罗方德联盟可能提前进入14nm量产,相比台积电的16nm制程具有优势。连张忠谋也坦承这一步台积电可能会落后,所以把希望寄托在2016年的10nm制程决战上。但是,三星与格罗方德联盟有可能受到产能不足困绕,为未来竞争平添了变数。而目前台积电已经拥有20nm制程产能达7万片/月。不管如何,高通与苹果的订单会成为争夺焦点,但是苹果的原则是不把鸡蛋放在同一个篮子里。

代工战场谁能胜出?

台积电在代工中独霸的态势,尽管近期内无法动摇它,但是会受到侵蚀。

代工业的成长不可能一蹴而成,其中台积电的老大地位不可动摇。尤其是2009年张忠谋第二次执掌公司以来,采用令人胆寒的积极投资扩张策略,在2010年~2013年期间总投资达300多亿美元,使得先进制程技术不断推进,再次稳固了代工龙头地位,并取得十分喜人的结果。

2013年台积电总产能约月产130万片(8英寸计),其中28nm产能为月产13万片(12英寸计),全球市占率按销售额计达80%。而且它的28nm爬坡速度非常快,2011年第四季度它的28nm刚刚启步,季销售额才1.5亿美元,至2012年年底已经占年销售额170亿美元的24%,达40.8亿美元,2013年年底占近200亿美元销售额的37%,达到65亿美元。

以每月6万片晶圆的产能来计算,台积电20nm制程晶圆的平均价格估计在2014年第四季度达到每片6000美元,与28nm晶圆平均价格(约4500美元~5000美元)相较有很大的提升。而估计其16nm/14nm的FinFET晶圆的生产成本约为每片4000美元,加上毛利率约45%,销售价格则为每片7270美元。如果台积电对于20nm制程的预测准确,从整体上看它的20nm制程的市占率,将会在2014年第四季度时达到全球的95%。

由此可以看出台积电代工老大地位不可动摇的原因:一是成品率高达90%,对手们可能约70%;二是拥有向客户提供支持的约6300项IP专利,业界戏称如有个“图书馆”一样;三是产能迅速到位,如28nm的产能达月产13万片,是格罗方德的3倍。

台积电在代工中独霸的态势,尽管近期内无法动摇它,但是一定会受到侵蚀,也即它不太可能维持住48%以上的高毛利率。其中的争夺既有16nm/14nm也有28nm代工。28nm目前仍是主战场,因为这一块的全球市场规模约有80亿美元~100亿美元。三星与格罗方德联盟的优势在于提出了FDSOI的28nm新工艺路线,对于要求更低功耗的芯片具有吸引力。另外,它们的代工价格一定会低于台积电。

至于联电与中芯国际的28nm,尽管它们都声称马上能准备好,但受限于产能,以及技术上的爬坡时间,想要获得大的突破,尚需时间。

另外,不可否认英特尔是个潜在对手。因为从工艺制程的技术水平以及研发投入上看,它肯定都是全球最领先的。但是,英特尔欲从IDM模式转向代工不是一件容易的事。一方面是把大量的产能转向代工,英特尔从思想上尚未下最后的决心,英特尔处理器的平均毛利率高达68%,代工厂毛利率可无法有那么高。另一方面,它缺乏代工所需配套的IP,这不是短期内就能准备就绪的。所以近期英特尔的高管透露了其意图,仅是通过代工来维持少数几个高利润率的客户。

产业格局前景难料

在16nm/14nm区段,台积电、三星、英特尔等各家,都不具备必胜把握。

与28nm代工产业不同,未来全球16nm/14nm及以下的代工格局前景难料。因为目前全球半导体业的现状是这样的:从技术上每两年前进一个工艺节点,理论值是2013年14nm及2015年10nm,可实际上英特尔的14nm量产推迟到了2014年第四季度,相比正常情况延长了两个季度。台积电更是灵巧,声言2014年是20nm量产及2015年才是16nm量产的时间点。三星电子推出先进代工制程14nmFinFET的应用处理器(AP)试制品,将先提供给高通、苹果、超微(AMD)等主要客户,但是目前它们的产能不足,三星才月产1万~1.5万片,格罗方德才3.5万片。两者加总才月产5万片。

更关键的是,目前10nm工艺制程都是处于研发阶段,包括英特尔、台积电及三星在内,离真正量产尚有距离,其中的变数还很多。最乐观的预测,10nm制程也要到2016年才能量产。另外,10nm制程之后,究竟如何往下走,尚不十分清楚,其中包括EUV何时准备好难以预言,10nm时193nm光刻工艺的成本与栅极材料的替代品的工艺等尚未完全就位。

按Gartner的观点,从近期来看,在1~2年内FinFET的量产,全球代工的产能需求不会超过月产5万片。而到2018年前也不会有大于月产25万片的市场需求。而这样的市场需求有两家大的代工厂已经足够,所以现在众多的一线代工厂纷纷进入FinFET工艺,未来一定会发现有人失声。

按PacificCrestSecurities的分析师的观点,从投资规模计,16nm/14nmFinFET技术投资1万片产能要12.7亿美元的投资,再增加2万片需25亿美元的投资。

还有一个不能言透的问题,技术方面谁能真正过关,即成品率能同步吗?据目前的态势,无论台积电的20nm量产还是英特尔的14nm量产,都出现了推迟的现象,都有成品率的问题存在其中。所以,未来究竟谁的技术真正过关还需观察。

客观地分析,英特尔占有一定优势。因为它从2011年的22nm节点就开始采用FinFET技术,至今已经是第二代了,经验相对多一些。否则也不可能发生原是台积电老客户的Altera,突然转向拥抱英特尔的14nm芯片代工的情况。还有,近期松下电子也下单给英特尔。足以证明其在技术方面可能高出一头。但是也不可否认,英特尔在代工方面尚有许多问题。所以在16nm/14nm这一区段,无论台积电、三星与格罗方德联盟,还是英特尔,哪家都不具备必胜的把握。

综上所述,未来全球16nm/14nm及以下的代工格局前景难料。

支付宝打赏

支付宝打赏  微信打赏

微信打赏