后FinFET时代,晶体管将走向何方?

编者按:进入最近两个月,因为三星3nm的大进步,还有台积电宣布在5nm乃至3nm进展,2nm规划,这就引发了大家对晶体管未来的担忧。那么究竟到了1nm之后,制程世界需要怎样的支持?未来的工艺技术又会走向何方?我们来看一下IMEC专家的分享。

FinFET晶体管结构是当今半导体行业的主力。但是,随着微缩的继续,人们不希望出现的短沟道效应需要引入新的晶体管结构。在本文中,imec的3D混合微缩项目主管Julien Ryckaert勾勒出了向2nm及更高技术节点发展的演进之路。在这条激动人心的道路上,他介绍了nanosheet晶体管、forksheet器件和CFET。这些想法的一部分已在2019年IEEE国际电子器件会议(IEDM)上发表。

FinFET:当今最先进的晶体管

在每一代新技术中,芯片制造商都能将晶体管规格缩小0.7倍,在器件层面上实现15%的性能提升、50%的面积增益、40%的功耗降低和35%的成本降低。几年前,业界为了维持这种微缩路径,从“老式”的平面MOSFET过渡到FinFET晶体管架构。在FinFET中,源极和漏极之间的沟道呈鳍状。栅极环绕这个3D沟道,从沟道的3个侧面进行控制。这种多栅极结构可以消除短沟道效应,短沟道效应会在栅极长度缩短时降低晶体管的性能。

出色的短沟道控制至关重要,因为它为器件微缩奠定了基础——允许更短的沟道长度和更低的工作电压。

2012年,首批商用22nm FinFET问世。从那时起,FinFET架构得到了改进,以提高性能和减少面积。例如,FinFET的3D特性允许增加鳍片高度,从而在相同的封装面积上获得更高的器件驱动电流。如今,工业界正在加紧生产“内含”FinFET的10nm/7nm芯片。在最先进节点的单元层面,标准单元的Track高度为6T(这是单元面积的量度标准),每个器件的鳍片数量低至2个。

垂直堆叠的nanosheet:进化的一步

但随着微缩至5nm以下,预计FinFET将失效。在减小栅极长度时,FinFET结构反过来不能提供足够的静电控制。除此之外,向更低Track高度标准单元的演进需要向单鳍片器件过渡,即使鳍片高度进一步增加,单鳍片器件也不能提供足够的驱动电流。

然而,随着技术节点的变化,半导体行业并不急于转向其他晶体管架构。一些公司甚至决定在某些节点上停留更长时间。但仍有一些应用——如机器学习、大数据分析和数据中心服务器——需要最新的“通用”CMOS解决方案。利用这种通用的CMOS解决方案,在同一个技术节点中的同一个晶体管结构可以用于执行芯片上的所有功能。

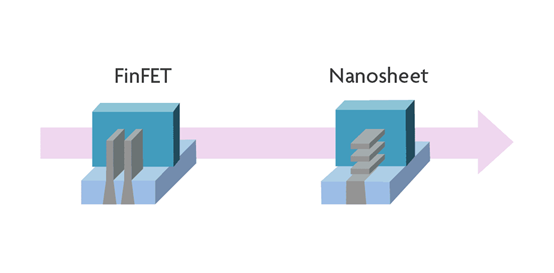

此处,垂直堆叠的nanosheet晶体管可以救急。它们可以被认为是FinFET器件的自然进化。想象一下,将一个FinFET侧放,然后将其分成独立的水平薄片,这些薄片构成了沟道。现在,一个栅极完全环绕在沟道上。与多栅极FinFET相比,nanosheet的这种栅极全包的特性提供了更出色的通道控制能力。同时,沟道横截面在3D体积中的更优化分布,优化了单位面积的有效驱动。

从FinFET到nanosheet的自然进化

对于微缩助推器的需求

在6T和5T的低单元Track高度下,向nanosheet器件的迁移成为最佳选择,因为此时鳍片的减少会降低传统的基于鳍片的场效应晶体管的单元中的驱动电流。

但是,如果不引入结构化的缩放助推器,如埋入式电源线和环绕式触点,就不可能将Track高度(以及单元面积)从6T降低到5T。

电源线(Power rails)为芯片的不同组件供电,传统上在芯片的BEOL(即Mint层和M1层)中以金属线的形式实现。然而,在那里,它们占据了相当大的空间。在埋入式电源线结构中,电源线埋在芯片的前端线路中,以帮助释放互连的走线资源。此外,它们为因节距微缩而导致BEOL电阻增加的技术提供了较低的电阻局部电流分布。通过从后道工序移除电源线,标准单元高度可以从6T进一步降低到5T。

下一步:缩小p和n之间的间距

随着track高度越来越小,进一步降低单元高度将要求单元内nFET和pFET器件之间的间距更加紧密。然而,对于FinFET和nanosheet器件来说,工艺限制限制了这些n和p器件的结合。例如,在FinFET架构中,n和p之间通常需要2个虚拟鳍片间距,消耗了高达40~50%的总可用空间。

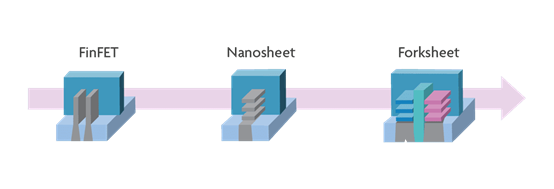

为了扩展这些器件的可微缩性,IMEC最近提出了一种创新的替代架构,称为forksheet器件。forksheet可认为是nanosheet器件的自然延伸。

与nanosheet器件相反,这些sheet现在由分叉的栅极结构控制,这是通过在pMOS和nMOS器件之间引入介质层来实现的。该介质层让p栅极沟槽与n栅极沟槽实现物理隔离,从而允许更紧密的n到p间距。

从FinFET到nanosheet,再到forksheet的自然演化。

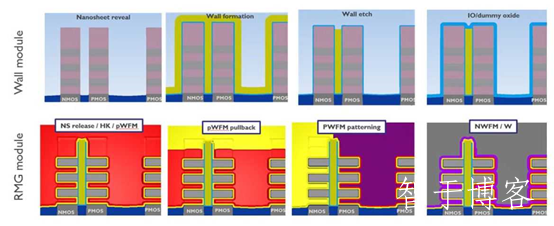

用于制造forksheet器件的工艺流程类似于用于制造nanosheet器件的工艺流程,只有几个额外的工艺步骤。n和p之间的介电隔离甚至有一些工艺上的优点,例如,填充功能金属的工艺更加简化。除了这一制程窗口的增强之外,由于n-p分离的大幅减少,forksheet预计将具有更卓越的面积和性能可微缩性。