芯片制造-半导体工艺教程

芯片制造-半导体工艺教程

Microchip Fabrication

----A Practical Guide to Semicondutor Processing

目录:

第一章:半导体工业[1] [2] [3]

第二章:半导体材料和工艺化学品[1] [2] [3] [4] [5]

第三章:晶圆制备[1] [2] [3]

第四章:芯片制造概述[1] [2] [3]

第五章:污染控制[1] [2] [3] [4] [5] [6]

第六章:工艺良品率[1] [2]

第七章:氧化

第八章:基本光刻工艺流程-从表面准备到曝光

第九章:基本光刻工艺流程-从曝光到最终检验

第十章:高级光刻工艺

第十一章:掺杂

第十二章:淀积

第十三章:金属淀积

第十四章:工艺和器件评估

第十五章:晶圆加工中的商务因素

第十六章:半导体器件和集成电路的形成

第十七章:集成电路的类型

第十八章:封装

附录:术语表

#1 第一章 半导体工业--1

芯片制造-半导体工艺教程 点击查看 章节目录

概述

本章通过历史简介,在世界经济中的重要性以及纵览重大技术的发展和其成为世界领导工业的发展趋势来介绍半导体工业。并将按照产品类型介绍主要生产阶段和解释晶体管结构与集成度水平。

目的

完成本章后您将能够:

1. 描述分立器件和集成电路的区别。

2. 说明术语 “固态,” “平面工艺”,““N””型和“P”型半导体材料。

3. 列举出四个主要半导体工艺步骤。

4. 解释集成度和不同集成水平电路的工艺的含义。

5. 列举出半导体制造的主要工艺和器件发展趋势。 一个工业的诞生

电信号处理工业始于由Lee Deforest 在1906年发现的真空三极管。1真空三极管使得收音机, 电视和其它消费电子产品成为可能。它也是世界上第一台电子计算机的大脑,这台被称为电子数字集成器和计算器(ENIAC)的计算机于1947年在宾西法尼亚的摩尔工程学院进行首次演示。

这台电子计算机和现代的计算机大相径庭。它占据约1500平方英尺,重30吨,工作时产生大量的热,并需要一个小型发电站来供电,花费了1940年时的400, 000美元。ENIAC的制造用了19000个真空管和数千个电阻及电容器。

真空管有三个元件,由一个栅极和两个被其栅极分开的电极在玻璃密封的空间中构成(图1.2)。密封空间内部为真空,以防止元件烧毁并易于电子的====移动。

真空管有两个重要的电子功能,开关和放大。 开关是指电子器件可接通和切断电流; 放大则较为复杂,它是指电子器件可把接收到的信号放大,并保持信号原有特征的功能。

真空管有一系列的缺点。体积大,连接处易于变松导致真空泄漏、易碎、要求相对较多的电能来运行,并且元件老化很快。ENIAC 和其它基于真空管的计算机的主要缺点是由于真空管的烧毁而导致运行时间有限。

这些问题成为许多实验室寻找真空管替代品的动力,这个努力在1947年12月23曰得以实现。贝尔实验室的三位科学家演示了由半导体材料锗制成的电子放大器。

这种器件不但有真空管的功能,而且具有固态(无真空)、体积小、重量轻,、耗电低并且寿命长的优点,起初命名为 “传输电阻器”而后很快更名为晶体管(transistor)。

John Barden, Walter Brattin 和William Shockley, 这三位科学家因他们的这一发明而被授予1956年的诺贝尔物理奖。

固态时代

第一个晶体管和今天的高密度集成电路相去甚远,但它和它的许多著名的后裔赋予了固态电子时代的诞生。除晶体管之外, 固态技术还用于制造二极管、电阻器和电容器。二极管为两个元件的器件在电路中起到开关的作用;电阻器是单元件的器件承担限制电流的作用.;电容器为两个元件的器件在电路中起存储电荷的作用,在有些电路中应用这种技术制造保险丝。有关这些概念和器件工作原理的解释请参见第14章。

这些每个芯片中只含有一个器件的器件称为分立器件(图1.4)。大多数的分立器件在功能和制造上比集成电路有较少的要求。大体上,分立器件不被认为是尖端产品,然而它们却用于最精密复杂的电子系统中。在1998年它们的销售额占全部半导体器件销售额的12%。2到20世纪50年代的早期半导体工业进入了一个非常活跃的时期,为晶体管收音机和晶体管计算机提供器件。

集成电路

分立器件的统治地位在1959年走到了尽头。那一年,在得州仪器公司工作的新工程师 Jacky Kilby 在一块锗半导体材料上制成了一个完整的电路。他的发明由几个晶体管、二极管、电容器和利用锗芯片天然电阻的电阻器组成。这个发明就是集成电路(integrated circuit),第一次成功地在一块半导体基材上做出完整的电路。

Kilby的电路并不是现今所普遍应用的形式,它是经Robert Noyce,然后最终在Fairchild Camera完成的。图1.5是Kilby的电路,我们可以注意到器件是用单独的线连接起来的。

早些时候在Fairchild Camera的Jean Horni 就已经开发出一种在芯片表面上形成电子结来制做晶体管的平面制作工艺(图1.6)。平面形式是利用了硅易于形成氧化硅并且为非导体(电绝缘体)的优点。Horni的晶体管使用了铝蒸汽镀膜并使之形成适当的形状来作器件的连线,这种技术称为平面技术(planar technology)。

Horni应用这种技术把预先在硅表面上形成的器件连接起来。

Kilby和Horni的集成电路成为所有集成电路的模式,这种技术不仅符合当时的需要,而且也是小型化和推动工业发展的生产有效成本制造业的根源。Kilby和Horni共同享有集成电路的专利。

图1.5 Kibly书中记载的集成电路

工艺和产品趋势

从1947年开始,半导体工业就已经呈现出在新工艺和工艺提高上的持续发展。工艺的提高导致了具有更高集成度和可靠性的集成电路的产生,从而推动了电子工业的革命。这些工艺的改进归为两大类:工艺和结构。工艺的改进是指以更小尺寸来制造器件和电路,并使之具有有更高的密度,更多数量和更高的可靠性。结构的改进是指新器件设计上的发明使电路的性能更好,实现更佳的能耗控制和更高的可靠性。

集成电路中器件的尺寸和数量是IC发展的两个共同标志。器件的尺寸是以设计中最小尺寸来表示的,叫做特征图形尺寸, 通常用微米来表示。一微米为1/10,000厘米或约为人头发的1/100。

英特尔公司的创始人之一Gordon Moore在1964年预言集成电路的密度会每十八个月翻一番,这个预言后来成为著名的摩尔定律并被证明十分准确(图1.7)。

集成度水平表示电路的密度,也就是电路中器件的数量。集成度水平(integration level)(图1.8)的范围从小规模集成(SSI)到超大规模(ULSI)集成电路,ULSI集成电路有时称为甚大规模集成电路(VVLSI). 大众刊物上称最新的产品为百万芯片(megachips)。

除集成规模外,存储器电路还由其存储比特的数量来衡量(一个4兆的存储器可存储四百万比特),逻辑电路的规模经常用栅极(栅极是逻辑电路中基本的功能元件)的数量来评价。

#1 第一章 半导体工业—2

Quote: |

| 芯片制造-半导体工艺教程 点击查看 章节目录

|

特征图形尺寸的减小

从小规模集成电路发展到今天的百万芯片,其中单个元件特征图形尺寸的减小起了重要的推动作用。这得益于光刻和多层连线技术的极大提高。图1.9为二十五年中实际和预期的特征图形尺寸的情况。半导体工业协会(SIA)预期到2012年特征图形尺寸会减小至50纳米(0.05微米)。3 元件尺寸的减小所带来的好处是电路密度的增加。

我们可以用一个家庭住宅区的布局做个比喻来解释这个发展趋势。住宅区的密度就取决于房屋大小, 占地大小和街道宽度。如果要居住更多的人口,我们可以增加住宅区的面积(增加芯片区域),另一种可能则是减小单个房屋的尺寸并使它们占地较小。我们也可以用减小街道大小的办法来增加密度,然而, 到一定程度时街道就不能再被减小了,或是就不够汽车通行的宽度了,而要保持房子的可居住性,房屋也不能无限制地减小,此时一个办法就是用公寓楼来取代单个房屋。所有的这些办法都应用在了半导体技术中。

特征尺寸的减小和电路密度的增大带来了很多益处。在电路的性能方面是电路速度的提高,传输距离的缩短和单个器件所占空间的减小使得信息通过芯片时所用的时间缩短,这种更快的性能使那些曾经等待计算机来完成一个简单工作的人受益非浅。电路密度的提高还使芯片或电路耗电量更小,要小型电站来维持运行的ENIAC已被靠使用电池的功能强大的便携式电脑所取代。

芯片和晶圆尺寸的增大

芯片密度从SSI发展到ULSI的进步推动了更大尺寸芯片的开发。分立器件和SSI芯片边长平均约为100mils(0.1英寸), 而ULSI芯片每边长为500 mils(0.5英寸)或更大。IC是在称为晶圆(wafer)的薄硅片(或其它半导体材料薄片)上制造成的。在圆形的晶圆上制造方形或长方形的芯片导致在晶圆的边缘处剩余下一些不可使用的区域,当芯片的尺寸增大时这些不可使用的区域也随之增大。为了弥补这种损失,半导体业界采用了更大尺寸的晶圆。随着芯片的尺寸增大, 1960年时的1英寸直径的晶圆已经被200毫米和300毫米(8英寸和12英寸)的晶圆所取代。

缺陷密度的减小

随着特征图形尺寸的减小,在制造工艺中减小缺陷密度和缺陷尺寸的需要就变得十分关键。在尺寸为100微米的晶体管上有一个1微米的灰尘可能不是问题,但对于一个1微米的晶体管来说会是一个导致元件失效的致命缺陷(图1.11)。正因为如此,污染控制的需要使得建造一个IC制造厂的花费升至十亿美元。

内部连线水平的提高

元件密度的增加带来了连线问题。在住宅区的比喻中, 用来增加密度的策略之一是减小街道的宽度,但是到一定的程度时街道对于汽车的通行来说就会太窄。同样的事情也会发生在IC设计中,元件密度的增加和紧密封装减小了连线所需的空间。解决方案是在元件形成的表面上使用多层绝缘层和导电层相互叠加的多层连线。

SIA的发展方向

主要的IC参数是相互关连的。摩尔定律预言了未来元件的密度,由此引发了集成度水平(元件密度)、芯片尺寸、缺陷密度(和尺寸)和所要求的内部连线数量水平的计算。半导体工业协会以一系列“路线图”的形式对这些及其它关键器件和产品参数的未来作了展望。

孔连接 M1=第一层金属 M2=第二层金属

图 1.12 经过平面化工艺具有两金属的VLSI典型结构的横切面, 它显示了经过平面化工艺后孔深的范围. (经Solid State Technology允许)

芯片成本

也许工艺和产品提高所带来的最大影响就是芯片的成本。图1.14展示了80年代时存储器芯片的成本逐年下降的情况。对于任何成熟的产品这个曲线都有代表性。价格开始时高,但随着技术的成熟和制造效率的提高价格会下降并最终达到稳定。虽然芯片的性能提高了,但价格却在持续地下降。在开始的30年中,半导体工业受到过2到5次经济冲击,这与铁路工业受到的冲击在同一时期。4影响芯片成本的因素将会在第15章讨论。

成本降低和性能提高这两个因素推动了固态电子在产品中的使用。到90年代时, 一个汽车所有的计算能力已经超过了第一架月球太空探测器,个人计算机更是令人鼓舞。今天,中等价位的台式机便有IBM在1970年制造的大型机的计算能力。图1.15说明了芯片的主要工业用途。 到2008年时, 全世界工业生产的晶体管将达到每个人十亿。5

半导体工业的发展

在整体上, 半导体工业一直在全世界范围连续增长。从它50年代诞生时起,它在全世界每年的销售额正在接近2000亿美元,其相应的供应商产业超过了300亿美元。6有趣的是, 虽然半导体工业显示出了成熟的迹象,但其增长速度还是高于其它成熟工业,这说明了它仍有很大的发展潜力。(图1.16)

图1.17为DRAM性能提高的一个例子,说明了多少卷的大百科全书可以被存储在更大容积的DRAM芯片中。

半导体工业的连续发展与进步使之在90年代中期时占据了世界主导地位,并超过汽车工业成为美国附加值最高的工业(图1.18)。

半导体工业的构成

电子工业可分为两个主要部分:半导体和系统(或产品)。半导体包括材料供应商、电路设计、芯片制造和半导体工业设备及化学品供应商。系统部分包括设计和生产众多基于半导体器件的、涉及到从消费类电子产品到太空飞船的产品。电子工业还涵盖了印刷电路板制造商。

半导体产业由两个主要部分组成。一部分是制造半导体固态器件和电路的企业,生产过程称为晶圆制造(wafer fabrication)。在这个行业中有三种类型的芯片供应商,一种是集设计、制造、封装和市场销售为一体的公司;另一种是做设计和晶圆市场的公司,它们从晶圆代工厂购买芯片;还有一种是晶圆代工厂, 它们可以为顾客生产多种类型的芯片。

以产品为终端市场的生产商和为内部使用的生产商都生产芯片。以产品为终端市场的生产商制造并在市场上销售芯片,以产品为内部使用的生产商它们的终端产品为计算器、通讯产品等等,生产的芯片用于它们自己的终端产品,其中一些企业也向市场销售芯片。还有一些生产专业的芯片内部使用,在 市场上购买其它的芯片。在80年代, 在以产品为内部使用的生产商中进行的芯片制造的比例有上升的趋势

#1 第一章 半导体工业—3

生产阶段

固态器件的制造有四个不同的阶段。(图1.19) 它们是材料准备、晶体生长和晶圆准备、晶圆制造、封装。

在第一个阶段,材料准备(见第二章)是半导体材料的开采并根据半导体标准进行提纯。硅是以沙子为原料通过转化成为具有多晶硅结构的纯硅(图1.21)。

在第二个阶段,材料首先形成带有特殊的电子和结构参数的晶体,再进行晶体生长,之后,在晶体生长和晶圆准备(见第三章)工艺中,晶体被切割成称为晶圆的薄片,并进行表面处理(图1.21)。另外半导体工业也用锗和不同半导体材料的混合物来制作器件与电路。

材料准备 晶体生长与晶圆准备 晶圆制造 封装

第三个阶段是晶圆制造,也就是在其表面上形成器件或集成电路。在每个晶圆上通常可形成200到300个同样的器件,也可多至几千个。在晶圆上由分立器件或集成电路占据的区域叫做芯片。晶圆制造也可称为制造、FAB、芯片制造或是微芯片制造。晶圆的制造可有几千个步骤,它们可分为两个主要部分:前线工艺是晶体管和其它器件在晶圆表面上的形成;后线工艺是以金属线把器件连在一起并加一层最终保护层。

遵循晶圆制造过程,晶圆上的芯片已经完成,但是仍旧保持晶圆形式并 且未经测试。下一步每个芯片都需要进行电测(称为晶圆电测)来检测是否符合客户的要求。晶圆电测是晶圆制造的最后一步或是封装(packaging)的第一步。

二氧化硅(沙子) 含硅气体 硅反应炉 多晶硅

1.20 二氧化硅到半导体应用级硅的转化

多晶硅 硅晶体生长 硅晶圆

封装通过一系列的过程把晶圆上的芯片分割开然后将它们封装起来。封装起到保护芯片免于污染和外来伤害的作用,并提供坚固耐用的电气引脚以和电路板或电子产品相连。封装是在半导体生产厂的另一个部门来完成的。

绝大数的芯片是被单个地封装起来的,但是混合电路、多芯片模块(MCMs)或直接安装在电路板上(COB)的形式正在日趋增加。混合电路是在陶瓷基片上将半导体器件(分立和IC)和厚或薄膜电阻及导线还有其它电子元件组合起来的形式,这些技术将在第18章中作出解释。

开发的十年(1951-1960)

虽然固态电子的极大优点早已为人所知,但小型化带来的优越性直到20年后才被认识到。在二十世纪五十年代,工程师开始着手工作并制定了许多今天仍在使用的基本工艺和材料。

使半导体器件工作的结构是 “PN结”(图1.24),它由富含电子的区域(负极或N型)和相邻的富含空穴的区域(失去电子有正电性或P型)一起构成的(见第11章)。

晶体管要有两个结才能工作(见第16章)。早期商业化的晶体管是双极型的,并且到二十世纪七十年代一直占据统治地位。双极是指晶体管具有工作在正电流和负电流情况下的结构。其它制作固态晶体管的主要方法是场效应管(FET),William Shockley在1951公布了FET的工作原理。这种晶体管只用一种类型电流来工作所以又叫做单极器件。后来大量上市的FET是具有以一种称为金属氧化物(MOS)结构的晶体管。

William Shockley和贝尔实验室对半导体技术的传播有不可磨灭的功绩。Shockley在1955年离开了贝尔实验室并在加利福尼亚的Palo Alto创建了Shockley实验室。虽然他的实验室未能幸存下来,但是它在西海岸建立了半导体制造业并为后来著名的硅谷的奠定了基础。贝尔实验室对它的半导体技术授以许可证并转给制造公司, 这促进了半导体工业的腾飞。

早期的半导体器件是用锗材料来制造的。得州仪器公司在1954年引入了第一个硅晶体管改变了这一趋势。而在1956和1957年贝尔实验室的两个技术进步,扩散结和氧化掩膜平息了哪种材料会占主流的问题。

氧化掩膜的发展带来了硅的时代。二氧化硅(SO2)可在硅表面上均匀地生成,并且有和硅相近的膨胀系数,使得在进行高温处理时不会出现翘起变形, 二氧化硅还是绝缘材料可在硅表面上充当绝缘物。另外,它对形成N和P型区所需的掺杂物有良好的阻挡作用。

由于这些技术的进步,Fairchild Camera在1960年引入了平面技术。使用上面提到的技术可在制造过程中形成(扩散)和保护(二氧化硅)PN结。氧化掩膜的发展也使得可通过晶圆的表面形成两个PN结(图1.26),也就是它们都在一平面中。这种工艺将半导体技术引入了Robert Noyce的用薄膜连线的时代。

通过刻有图案的氧化层对晶圆参杂

金属导电层

图1.25 基本的硅平化工艺

双极型晶体管

外延层

晶圆

1.26 在外延层上形成的两次渗透的双极型晶体管

贝尔实验室又构思出了在晶圆的表面沉积一层称为外延层的高纯度膜,再在其上形成晶体管的技术(图1.27),使用这种技术可制做出更高速度的晶体管,并提供了一个使得在双极电路中元件封装更紧密的方案。

五十年代的确是半导体发展的黄金时期,几乎所有基本的工艺和材料都是在这个非常短的时期内开发出来的。在这十年里,由开始用锗材料制造小量的简单器件,发展到奠定了半导体未来的第一块集成电路和硅材料的基础。

工艺的十年(1961-1970)

二十世纪六十年代是工艺工程师和公司创建的时代。在五十年代价格下降的趋势就开始形成了,在六十年代, 涌现出许多新的芯片制造商,这使得工艺工程师需要开发高产量的工艺来制造低价格的芯片。在这十年里,技术随着工程师在硅谷、波士顿的128号路区域以及得克萨斯州的不同公司间的流动而传播。

在五十年代, 多数的半导体制造设备是由芯片制造商内部制造或改装的,同样,多数的化学品也是在按工业级水平采购而后在内部进行 “清洁”。 到了六十年代,芯片制造厂的数量猛增,并且工艺接近了吸引半导体特殊供应商的水平。

五十年代的许多关键人物创建了新公司。Robert Noycee 离开了Fairchild 建立了英特尔(与Andrew Grove,Gorden Moore一起), Charles Sporck也离开了Fairchild开始经营国家半导体公司,Signetics 成为了第一家专门从事IC制造的公司。新器件设计通常是公司开始的动力,然而, 价格的下跌是一个残酷的趋势,会将许多新老公司驱逐出局。

价格的下跌由于1963年时的塑封在硅器件上的使用而加速,也在同一年,RCA宣布开发出了绝缘场效应管(IFET),这为MOS工业的发展铺平了道路。RCA还制造出了第一个互补型MOS(CMOS)电路。

在七十年代,半导体制造从实验室小批量发展到了生产线的大批量制造,也形成了产量与利润之间的关系。

产品的十年(1971-1980)

在二十世纪七十年代的开始,半导体IC的制造主要在MSI的水平,向有利润并高产的LSI的发展在某种程度上受到了膜版引起的缺陷和由接触光刻机(Conact Aligner)造成的晶圆损伤的阻碍。事实上,现存的所有工艺在一方面或另一方面都代表着是更高水平电路产品的量产的障碍。

PERKIN和ELMER公司开发出了第一个实际应用的投射光刻机,从而解决了膜版和光刻机的缺陷问题。在这十年中,洁净间的结构和运行得到了提高,并出现了离子注入机, 用于高质量膜版的E-BEAM机, 用于晶圆光刻的膜版步进式光刻机(Stepper)开始出现。

工艺过程的自动化从SPIN/BAKE和DEVELOP/BAKE开始,从操作员控制发展到工艺过程的自动控制提高了产量和产品的一致性。对基于设备的工艺的依靠使得半导体工业水平上升到新高度,工业的销售额上升至每年100亿美元。

当工艺与设备结合时,这个时期的发展就面向了全世界,随着工艺的提高对固态器件物理有了更细致的理解,这使得全世界学习这一工艺的学生,未来的工程师们也掌握了这一技术。

自动化的十年(1981-1990)

来自市场的压力成为工艺过程自动化首要动力,其次是越来越多的工艺步骤。特征图形尺寸的每次减小都会带来新问题,如更多的金属层要求更多的工艺步骤。机器会按照预先设好的步骤自动处理晶圆,然后再回到传输器中。大多数的工艺实现自动化后,在二十世纪八十年代的焦点是在如何生产区域去掉操作工和如何实现材料的自动运输。由于人是主要污染源,所以要求将操作工减到最少;最严密的规程也不能控制人员搬移晶圆时产生的微粒污染,这些问题将在第4章中做详细介绍。单个工艺的自动化使半导体工业面临开发在各种机器间传输晶圆的方法的挑战。 这方面的问题成了自动化十年的重点,以达到无人化的目标。

当大多数工业向制造标准化发展的时候,半导体工业却正好相反。虽然大多数晶圆厂具有较好的控制和特性,但同时, 各种趋势促使制造商设计更加复杂的芯片,新设计又给制造商提出新的挑战而导致新工艺的开发。在这些精密复杂的水平上,就需要机器的自动化来完成工艺控制和重复性。

二十世纪八十年代开始时美国和欧洲占统治地位,日本半导体生产商的崛起,半导体工业成为世界范围的工业,随之而来的是“四小虎”香港, 台湾, 新加坡和南韩半导体工业的发展。

产品的纪元(1991-2000)

从二十世纪七十到八十年代, 1微米特征图形尺寸的障碍显示了机遇和挑战,机遇是指这会是一个具有极高的速度和存储能力芯片的纪元。挑战是传统光刻由于增加的表面步骤、新增层和晶圆尺寸增大造成的局限。1微米的障碍是在实验室突破的,到1990年50%的生产线在生产微米级和低于微米级的产品。7

工业发展到了成熟后,更多传统上的重点被放在生产和市场问题上。早期的盈利策略是走发明的途径,也就是总要把最新和最先进的芯片抢先推向市场,以获得足够的可支付研发和设计费用的利润。这种策略带来的利润可以克服良品率和低效率的问题。

工艺控制上的技术(竞争)和改进的传播把更多工业的重点转移到了产品问题上。几个主要的产能因素是:自动化、成本控制、工艺特性化与控制及人员效率。

控制成本的策略包括:设备成本关系的详细分析;新厂的布局(如集束机器);自动化机械手;晶圆隔离技术(WIT);计算机集成制造(CIM);先进完善的统计工艺控制;先进的测量仪器;及时库存系统, 及其它(见15章)

技术推动的因素, 特征图形尺寸减小, 晶圆尺寸增大, 和良品率的提高都存在客观的和统计上的限制。但是产能的提高(包含许多因素)是持续获利的源泉。晶圆工厂的投资巨大(10-30亿美元),其设备和工艺开发同样耗资巨大。在研发0.35微米以下的技术时,X-RAY和深紫外光(DUV)光刻或传统的光刻的改进都是巨大的花费,同样, 在生产中也花费巨大。

这并不是说技术进步停止了,正相反,许多在十年中会用到的技术还是未知或处在非常原始的发展状态。技术的提高正在变成演化性的而不是革命性的。工程师正在学会如何在以技术飞跃来解决问题之前,从工艺过程中挖掘生产力。这是工业成熟的另外一个信号。

可能这十年的主要技术改变就是铜连线。铝连线在几个方面显现出局限性,特别是和硅的接触电阻。铜是一种较好的材料但它不易沉积和刻蚀,它如果接触到硅会对电路造成致命的影响。IBM8开发出了可实用的铜工艺,并在90年代末几乎立刻被业界接受。

极小的纪元

微观技术在公众的感觉中意味着 “小”,在科学中是指十万分之一。因此,特征图形尺寸和栅极的宽度以微米来表示,如 0.018微米。纳米正在被广泛使用,上述的栅级宽度则为180纳米。9

在半导体协会1997年的国家技术发展路线图(National Technology Roadmap for semiconductors,NTRS)中,对半导体通向极小纪元的道路作了描绘。栅极的宽度到2012会达到50纳米,但这并不容易实现。随着器件尺寸变的更小会有一系列可预见的事情,优点是更快的运行速度和更高的密度。然而, 更小的尺寸要求更精密的工艺和设备。栅极区域是MOS晶体管非常关键的部分。

更小的栅极更易受污染的干扰,这将推动更洁净的化学品和工艺的发展。低度的污染要求更敏感的测量技术,表面的粗糙度也成为一个要控制的参数。随着器件之间的更加紧凑,需要更多层的金属连线层结构,而同时,要保持表面足够平以满足光刻的要求,这给平面技术带来了一定的压力。更多层的金属连线会带来更高的电阻。新金属材料,如铜也就成了需要。要取得这些进步就需要更洁净的制造厂,极为纯净的材料和化学品以及集束设备的使用,将对污染的暴露减至最小和并提高生产效率。

晶圆的直径将会达到450毫米以上,工厂的自动化水平也将遍及到机器之间,并且带有集成的工艺监测系统。更多高水平的工艺将会要求更高产量的晶圆制造厂,这些厂的成本到2005年将达到100亿。10来自巨大投资的压力迫使研发和建厂的速度更快。

到2012年, 半导体工业和集成电路会与现今大不相同,并将到达硅晶体管基本物理上的极限。随着许多对低端技术新用途需求的不断出现,硅工业还将会活跃,例如烤面包机和电冰箱不太可能使用最新的尖端产品。新材料会在实验室出现,混合物半导体,如镓/砷化物(GaAs)就是候选。技术如分子束(MBE)(12章)可能被用来一次一和原子的方式制作新材料。

可以毫无疑问地说随着材料和工艺的不断向前推进,半导体工业将继续是主导工业,也还可以毫无疑问地说IC的使用将继续以未知的方法改变我们的世界。

关键术语和概念

固体器件 集成电路

二极管 集成度/电路密度

电容 平化处理(工艺)

电阻 半导体制造的四个阶段

晶体管 芯片尺寸

分立器件 特征图形尺寸

晶圆 半导体材料

价格侵蚀 混合电路

复习问题

1. 列出四种类型的分立器件。

2. 描述固体器件相对于真空器件的优点。

3. 一块VLSI较一块ULSI集成电路有更多的元件。(对或错)

4. 描述混合电路与集成电路的区别。

5. 叙述制造晶圆的工艺阶段。

6. 叙述制造芯片的的工艺阶段。

7. 描述N/P的结构。

8. 描述术语录“特征尺寸”的含义。

9. 列出推动半导体工业的三个趋势。

10.描述半导体封装的功能

#1 第二章 半导体材料和工艺化学品-----1

第二章 半导体材料和工艺化学品-----1

概述

半导体材料拥有特有的电性能和物理性能,这些性能使得半导体器件和电路具有独特的功能。这些性能会和原子的基本性能、固体、本征半导体和掺杂半导体的电性能一同分析。在本章的第二部分,我们会讨论适用于工艺化学品的基础化学。

目的

完成本章后您将能够:

1.分清原子的各个部分。

2.说出掺杂半导体的两种特性。

3.列出至少三种半导体材料。

4.列出与硅相比,砷化镓的优缺点。

5.解释N型和P型半导体材料在组成和电性能方面的不同。

6.描述电阻率和电阻的特性。

7.指明酸,碱和溶剂的不同。

8.列出自然界的四种状态。

9.给出原子、分子和离子的定义。

10.解释至少四种化学品的安全操作规则。

原子结构

玻尔原子

要想理解半导体材料就必须了解原子结构的基本知识。

原子是自然界的基本构造单元。自然界中的任何事物都是由96种稳定12种不稳定的元素组成。每一种元素都有不同的原子结构,不同的结构决定了元素的不同特性。

黄金的特性也是由黄金的原子结构决定的。如果一块黄金不断地被分割而变小,那么最终会留下一小块,依然能呈现出黄金的特性,这一小块就是原子。

进一步分下去,就会产生组成每个原子的三个部分。它们被称作亚原子粒子,也就是质子,中子和电子。这些亚原子粒子各有其特性。要组成金原子就要求这些亚原子粒子有特定的组合和结构。著名物理学家尼尔斯•玻尔最早把原子的基本结构用于解释不同元素的不同物理、化学和电性能(图2.1)。

e-=电子

+=质子

N=中子

O=未填充电子位置

图2.1 玻尔原子模型

在玻尔的原子模型中,带正电的质子和不带电的中子集中在原子核中,带负电的电子围绕原子核在固定的轨道上运动,就象太阳的行星围绕太阳旋转一样。带正电的质子和带负电的电子之间存在着吸引力,不过吸引力和电子在轨道上运行的离心力相抵,这样一来原子结构就稳定了。

每个轨道容纳的电子数量是有限的。在有些原子中,不是所有的位置都会被电子填满,这样结构中就留下一个“空穴”。当一个特定的电子轨道被填满后,其余的电子就必须填充到下一个外层轨道。

元素周期表

不同的元素,其原子中的电子、质子和中子数是不同的。幸运地是,自然界把这些亚原子粒子有序地组合起来。如果对决定原子结构的一些规则进行研究,就会对理解半导体材料和工艺化学品的特性有帮助。原子(也是元素)的范围包括从最简单的氢原子(有一个电子)到最复杂的铹(有103个电子)。

氢原子只包括一个原子核中的质子和一个电子。这种组合解释了原子结构的第一条规则。

1.在任何原子中都有数量相等的质子和电子。

2.任何元素都包括特定数目的质子,没有任何两种元素有相同数目的质子。氢在原子核中有一个质子,而氧原子有八个。

这条规则引出了人们对每种元素指定特定的序数的做法,“原子序数”就等于原子中质子的数目(也就是电子的数目)。元素的基本参照就是元素周期表(图2.2)。周期表中每种元素都有一个方格,内有两个字母。原子序数就在方格的左上角。钙 (Ca)的原子序数为20,所以我们立即知道钙原子核中有20个质子,轨道系统上有20个电子。

中子是中性不带电粒子,和质子一起构成原子核。

图2.3表示出了一号元素氢,三号元素锂和十一号元素钠的原子结构图。当建立这些结构图的时候,就可以观察到电子在合适的轨道上分布的规则。该规则就是每个轨道(n)只能容纳2n2 个电子。按此算法,一号轨道只能容纳2个电子。该规则迫使锂的第三个电子进入第二个轨道。第二个轨道的电子数受该规则限制最多有8个,第三轨道的电子数最多有18个。因此在建立有11个质子和电子的钠原子的结构图时,开始的两个轨道容纳了10个电子,第十一个电子就留在第三个轨道上。

这三个原子有一个共性,每种原子的最外层都只有一个电子,这显示出了元素的另外一个可观察到的事实。

2.2 元素周期表

第一号元素:氢

第三号元素:锂

第十一号元素:钠

图2.3 氢、锂和钠的原子结构

1.有相同最外层电子数的元素有着相似的性质,这个规则就反映在周期表中。注意氢、锂和钠都出现在标着罗马数字I 的竖列中,这个竖列数就代表最外层的电子数,每一列的元素都有着相似的性质。

2.最外层被填满或者拥有八个电子的元素是稳定的,这些原子在化学性质上要比最外层未填满的原子更稳定。

3. 原子会试图与其它原子结合而形成稳定的条件¾¾各轨道被填满或者最外层有八个电子。

如掺杂半导体这一节所阐述的,规则4和5影响着N型和P型半导体材料的形成。

#1 第二章 半导体材料和工艺化学品---2

第二章 半导体材料和工艺化学品---2

电传导

导电子

很多材料的一个重要的特性就是导电或者支持电流。电流其实就是电子的流动。如果元素或者材料中的质子对外层的电子的束缚相对较弱,电传导就可以进行。在这样的材料中,这些电子可以很容易地流动和建立电流,这种情况存在于大多数金属中。

材料的导电性用一个叫做导电率的因素来衡量。导电率越高,材料的导电性越好。导电能力也用导电率的倒数,即电阻率来衡量。材料的电阻率越低,相应导电能力也越好。

C=1/ρ

3个导体分别为铜、银、金

图2.4 三个最好的电导体

其中C=导电率

ρ=单位为欧姆-厘米(Ω-cm)的电阻率

绝缘体和电容器

与导电性相对的是,有些材料中表现出核子对轨道电子的强大的束缚,直接的效果就是对电子移动有很大的阻碍,这些材料就是绝缘体。它们有很低的导电率和很高的电阻率。在电子电路和产品中,绝缘体如二氧化硅用作绝缘。

象做三明治那样把一层绝缘体夹在两个导体之间就形成了一种电子设备即电容。在半导体结构中,MOS栅结构,被绝缘层隔开的金属层和硅基体之间和其它结构中都存在电容(参看第16章)。电容的实际效用就是存储电荷。电容在存储器中用于信息存储,消除在导体和硅表面垒集的不利的电荷,并且形成场效应晶体管中的工作器件。薄膜的电容能力与其面积和厚度以及一个特性指数即绝缘常数。半导体金属传导系统需要很高的导电率,因而也就是需要低电阻和低电容材料。这些材料就是低绝缘常数的绝缘体,用于传导层间隔离的绝缘层需要高的电容或者高绝缘常数的绝缘体。

C = 电容

k =材料的绝缘常数

E0 = ====空间的介电常数(====空间有最高的电容)

A = 电容的面积

t = 绝缘材料的厚度

电阻

与导电率程度(和电阻率)相关的电因子就是特定体积材料的电阻。电阻是材料电阻和尺寸的因子,如图2.5所示,电流的电阻由欧姆来衡量。

R=电阻

L=长度

W=宽度

D=高度

A=横截面积=WxD

P=材料电阻率

图2.5 长方形棒的电阻

公式定义了特定材料特定体积的电阻(在图中,体积由三个维度X,Y,Z的矩形)。这种关系类似于密度和重量,密度为材料的特性,重量为特定体积的材料所受的力。

电流类似与水管中的水流。对于给定的水管直径和水压,只有一定量的水会流出水管,水流的阻力可以通过增加水管的直径,缩短水管和增加水压。在电子系统中,通过增大材料的横截面,缩短部件的长度,增大电压(类似于水压)和减小材料的电阻,可以增强电流。

本征半导体

半导体材料,顾名思义就是本身就有一些天然的导电能力的材料。有两种半导体元素——硅和锗,在元素周期表中位于第四列(如图2.6)。另外,还有好几十种化合物材料(化合物就是两个或更多元素化合的材料)也表现出半导体的特性.这些化合物源自第三列和第四列的元素,如砷化镓和磷化镓。其它化合物源自第二列和第六列的元素。

本征,该术语指的是材料处于纯净的状态而不是掺杂了杂质或其它物质。

Ge为元素半导体

3到5族化合物半导体

图2.6 半导体材料

掺杂半导体

半导体材料在其本征状态是不能用于固态元件的。但是通过一种叫做掺杂的工艺,可以把特定的元素引入到本征半导体材料中。这些元素可以提高本征本导体的导电性。掺杂的材料表现出两种独特的特性,它们是固态器件的基础。这两种特性是:

1.通过掺杂精确控制电阻率

2.电子和空穴导电

掺杂半导体的电阻率

金属导电率的范围在每欧姆厘米104到106之间,该范围的含义可通过对如图2.5所示的电阻进行测试得到。如果固定体积的金属的电阻率确定,改变电阻的唯一方法是改变金属的形状。而在有半导体特性的材料中,电阻率可以改变,从而在电阻的设计中增加了又一个====度。半导体就是这样的材料,其电阻率的范围可以通过掺杂扩展到10-3到103之间。

半导体材料可以掺杂一些元素以达到一个有用的电阻率范围,材料或者多电子(N型)或者多空穴(P型)。

图2.7显示出掺杂程度与硅的电阻率之间的关系。X轴标为载流子是因为材料中的电子或空穴叫做载流子。注意有两条曲线:N型与P型。这是因为在材料中移动一个电子或空穴所需的能量是不同的。如曲线所示,在硅中要达到指定的电阻率N型所需掺杂的浓度要比P型小。另一种方法来表示这种现象就是移动一个电子比移动一个空穴的能量要小。

横轴为电阻率,纵轴为载流子浓度,其中P为硼掺杂,N为磷掺杂

图2.7 硅的电阻率与掺杂(载流子)的浓度。

只需0.000001%到0.1%的掺杂物就可以使半导体达到有用电阻率范围。半导体的特性允许在材料中创建出非常精确电阻率的区域。

电子和空穴传导

金属传导的另一个限制就是它只能通过电子的移动来导电。金属永远是N型的。通过掺杂特定的掺杂元素,半导体可以成为N型或者P型。N型和P型半导体可以用电子或者空穴来导电。在了解传导机理之前,了解在半导体结构中====(多余)的电子或空穴的形成是有益的。

为理解N型半导体,如图2.8所示将很少量的砷(As)掺入硅(Si)中。假定即使混合后每一个砷原子也被硅原子所包围。使用2.3.2节的规则,原子试图通过在外层有八个电子来达到稳定,砷原子表现为与其邻近的硅原子共享四个电子。但是,砷来自第五族外层有五个电子,直接的结果是其中的四个与硅中的电子配对,最后一个留下来。这一个可以用来电子传导。

考虑到硅晶体中每立方厘米中有百万个原子,从而也就有很多电子可以用来导电。在硅中,掺杂元素砷,磷和锑会形成N型硅。

对P型材料的理解的方法是相同的。不同之处在于使用来自元素周期表第三族的硼来形成P型硅。当混入硅中,它也与硅原子共享电子。不过,硼只有三个外层电子,所以在外层会有一个无电子填充的位置。这个未填充的位置就叫做空穴。

多出的电子

图2.8 用砷来做N型掺杂的硅

空穴

图2.9 用硼来做P型掺杂的硅

在掺杂的半导体材料中有很多的活动:电子和空穴不停地形成。电子会被吸引入未填充的空穴,从而留下一个未填充的位置,也就是另一个空穴。

如图2.10解释了空穴是怎样导电的。当电压加在一段导电或半导电材料上时,负电子就移向电压的正极,就象电池一样。

在P型材料(图2.11),电子会沿t1的方向跃入一个空穴而移向正极。当然当它离开它的位置时,它也留下一个新的空穴。当它继续向正极移动时,它会形成连续的空穴。这种效果对于用电流表来衡量这个过程的人来说就是该材料支持正电流,而实际上它是负电流移向相反的方向。这种现象叫做空穴流(hole flow),是半导体材料所独有的。

图2.10 N型半导体材料中的电子传导

电子方向;空穴方向

图2.11 P型半导体材料中的空穴传导

在半导体材料中形成P型导电的掺杂剂叫做受主(acceptors)。在半导体材料中形成N型导电的掺杂剂叫做授主(donors)。记住这些术语一个简单的方法就是在受主中有一个p而授主中有一个n。

在图2.12中总结了导体,绝缘体和半导体的电特性。在图2.13中总结了掺杂半导体的特性。

使用特定的掺杂元素在锗和化合物半导体中也可形成N型和P型半导体。

[转贴]第二章 半导体材料和工艺化学品---3

by r53858

载流子迁移率

在2.5.6节提到过,在半导体材料中移动一个电子比空穴要容易。在电路中,我们对载流子(空穴和电子)移动所需能量和其移动的速度都感兴趣。移动的速度叫做载流子迁移率,空穴比电子迁移率低。在为电路选择特定半导体材料时,这是个非常值得考虑的重要因素 。

分类 电子 例子 导电率

1.导体 ====移动 金、铜、银

2.绝缘体 无法移动 玻璃、塑料

3.半导体a.本征的 有些可以移动 锗、硅、3到5族元素

B.掺杂的 受控的部分可以移动 N型半导体P型半导体

图2.12 材料的电分类

N型 P型

1.导电 电子 空穴

2.极性 负 正

3.掺杂术语 授主 受主

4.在硅中掺杂 砷、磷、锑 硼

图2.13 掺杂半导体的性质

半导体产品材料

锗和硅

锗和硅是两种重要的半导体,在最初固态器件时代,第一个晶体管是由锗制造的。但是锗在工艺和器件性能上有问题。它的937摄氏度熔点限制了高温工艺,更重要的是,它表面缺少自然发生的氧化物,从而容易漏电。

硅与二氧化硅平面工艺的发展解决了集成电路漏电问题,使得电路表面轮廓更平坦并且硅的1415摄氏度的熔点允许更高温的工艺。因此,世界上超过了90%的生产用晶圆的材料都是硅。

半导体化合物

有很多半导体化合物由元素周期表中第三族和第四族,第二族和第六族的元素形成。在这些化合物中,商业半导体器件中用得最多的是砷化镓(GaAs)和磷砷化镓(GaAsP),磷化铟(InP),砷铝化镓(GaAlAs)和磷镓化铟(InGaP)。1这些化合物有特定的性能。2当电流激活时,由砷化镓和磷砷化镓做成的二极管会发出可见的激光。这些材料用于电子面板中的发光二极管(LED’s)。

砷化镓的一个重要特性就是其载流子的高迁移率。这种特性使得在通讯系统中砷化镓器件比硅器件更快地响应高频微波并有效地把他们转变为电流。

这种载流子的高迁移率也是对砷化镓晶体管和集成电路的兴趣所在。砷化镓器件会同类硅器件快上两到三倍,应用于超高速计算机和实时控制电路如飞机控制。

砷化镓本身就对辐射所造成的漏电具有抵抗性。辐射比如宇宙射线会在半导体材料中形成空穴和电子,它会升高不想要的电流,从而造成器件或电路工作不正常或停止工作。可以在辐射环境下工作的器件叫做辐射硬化。砷化镓是天然辐射硬化。

砷化镓也是半绝缘的。这种特性使邻近器件的漏电最小化,允许更高的封装密度,进而由于空穴和电子移动的距离更短,电路的速度更快了。在硅电路中,必须建立在表面建立特殊的绝缘结构来控制表面漏电。这些结构使用了不少空间并且减少了电路的密度。

尽管有这么多的优点,砷化镓也不会取代硅成为主流的半导体材料。其原因在于性能和制造难度之间的权衡。虽然砷化镓电路非常快,但是大多数的电子产品不需要那么快的速度。在性能方面,砷化镓如同锗一样没有天然的氧化物。为了补偿,必须在砷化镓上淀积多层绝缘体。这样就会导致更长的工艺时间和更低的产量。而且在砷化镓中半数的原子是砷,对人类是很危险的。不幸的是,在正常的工艺温度下砷会蒸发,这就额外需要抑制层或者加压的工艺反应室。这些步骤延长了工艺时间,增加了成本。在晶体生长阶段蒸发也会发生,导致晶体和晶圆不平整。这种不均匀性造成晶圆在工艺中容易折断,而且也导致了大直径的砷化镓生产比硅落后(参照第三章)。

尽管有这些问题,砷化镓仍是一种重要的半导体材料,其应用也将继续增多,而且在未来对计算机的性能可能有很大影响。

锗化硅

与砷化镓有竞争性的材料是锗化硅。这样的结合把晶体管的速度提高到可以应用于超高速的对讲机和个人通讯设施当中。3器件和集成电路的结构特色是用超高真空/化学气象沉积法(UHV/CVD)来淀积锗层。4双极晶体管就形成在锗层上,不同于硅技术中所形成的简单晶体管,锗化硅需要晶体管具有异质结构(hetrostructures)和异质结(heterojunctions)。这些结构有好几层和特定的掺杂等级从而允许高频的运行(参照第十六章)。

主要的半导体材料和二氧化硅之间的比较列在图2.14中。

铁电材料

在对更快和更可靠的存储器研究中,铁电体成为一种可行的方案。一个存储器单元必须用两种状态中的一种(开/关,高/低,0/1)存储信息,能够快速响应(读写)和可靠地改变状态。铁电材料电容如PbZr1-xTxO3(PZT)和SrBi2Ta2O9(SBT)正好表现出这些特性。它们并入SiCMOS(参考第十六章)存储电路叫做铁电随机存储器(FeRAM)。5

Ge Si GaAs SiO2

原子质量

每立方厘米原子数或摩尔

晶体结构

单位晶格

密度

能隙

绝缘系数

熔点

击穿电压

热膨胀线性系数

图2.14 半导体材料的物理性能

工艺化学品

很明显,需要很多工艺来将原始半导体材料转变为有用的器件,大部份的工艺使用化学品。芯片制造首要是一种化学工艺,或者更准确地说是一系列化学工艺,高达20%工艺步骤是清洗和晶圆表面的准备。6

半导体工厂消耗大量的酸,碱,溶剂和水。为达到精确和洁净的工艺,部分成本是由于化学品需要非常高的纯度和特殊的反应机理。晶圆越大,洁净度要求越高,相应就需要更多的自动清洗位置,清洗所用化学品的成本也就跟着升高。当把芯片的制造成本加在一起,其中化学品占总制造成本可达40%。

对半导体工艺化学品洁净度的要求在第四章介绍。在工艺章节会详细介绍特定化学品和它们的特性。

分子,化合物和混合物

在2.3.1节,用玻尔原子模型解释物质的基本结构。这个模型可解释组成自然界所有物质的元素之间的结构差异,但是很显然自然界中超过了103(元素的数目)种物质。

非元素材料的基本单位是分子。水的基本单位是两个氢原子和一个氧原子组成的分子。材料的多样性源自原子之间相互结合形成分子。

每次我们想指定一个分子时就画一个如图2.15的图表是不方便的,更常用的方式是写出分子式。如水它就是熟悉的H2O。这个分子式确切地告诉我们在材料中的元素和其数目。化学家用更确切的术语“化合物”来描述由元素的不同组合。这样H2O(水),NaCl(氯化钠或盐),H2O2(过氧化氢)和As2O3(三氧化砷)都是由一个一个分子集合成的不同化合物。

有的元素结合成双原子分子,双原子分子是分子中有两个相同元素的原子。熟悉的气体如氧气、氮气和氢气在自然状态下都是由双原子分子构成的。这样它们的公式就是O2,N2和H2。

物质还有其它两种形式:混合物和溶液。混合物由两种或更多种物质构成,但每种物质都保留各自的特性。典型的混合物就是盐和胡椒粉。

溶液是固体溶解于液体中的混合物,在液体中,固体分散分布,呈现出独特的性能。不过溶液中的物质并没有形成新的分子。盐水就是溶液的一个例子,可以把它分解回其初始状态:盐和水。

图2.15 水分子图

离子

术语“离子(ion)”或“离子的(ionic)”经常在半导体工艺中使用。该术语指的是材料中任何电荷不平衡的原子或分子。离子是通过在元素或分子的化学符号后加上一个正或负号的上标(Na+,Cl-)。举例来说,一个很严重的污染问题就是可移动的离子污染比如钠(Na+)。当钠进入半导体材料或器件中,由于钠带正电荷而引起问题。但在某些工艺如离子注入工艺中,形成离子如硼离子(B+)对完成工艺是很必要的。

第二章 半导体材料和工艺化学品---4

物质的状态

固体,液体和气体

物质有四种状态:固体,液体,气体和等离子体(图2.16)。

**固体在常温常压下保持一定的形状和体积。

**液体有一定的体积但形状是变化的。一公升的水会与其容器形状一致。

**气体既无一定形状又无一定体积。它也会跟其容器形状一致,但跟液体不同之处是,它可扩展或压缩直至完全充满容器。

特定物质的状态与其压力和温度很有关系。温度是对材料中包含的所有能量的一种衡量。我们知道只需简单地改变其温度和(或)压力,水就可以在三种状态下存在(冰,液态水,蒸汽或水蒸气)。压力的影响更加复杂,超出了本文的讨论范围。

固体

液体

气体

等离子体

图2.16 物质的四种状态

等离子体

第四种状态就是等离子体。恒星就是一个典型的例子,它当然不符合固体,液体或气体的定义。等离子体是电离原子或分子的高能集合,在工艺气体上施加高能射频场可以诱发等离子体。它可用于半导体技术中促使气体混合物化学反应,它的一个优点就是它跟对流系统如烤箱里的对流加热相比,能量可以在较低的温度下传递。

物质的性质

所有物质都可用其化学组成和由化学组成而决定的性质来区分。在这一节,定义了好几个重要性质,都需要通过与半导体材料和工艺化学品打交道来理解的。

温度

不管是在氧化管中还是在等离子刻蚀反应室内,化学品的温度都对和其它化学品的反应发挥着重要影响,而且一些化学品的安全使用也需要了解和控制化学品的温度。有三种温度表示方法用于标识材料的温度,它们是华氏温标,摄氏温标和开氏温标(图2.17)。

水的沸点

水的冰点

绝对零度

图2.17 温度计量系统

华氏温标由德国物理学家Gabriel Fahrenheit用盐和水溶液开发的。他把溶液的冰点温度定为华氏零度,不幸地是纯水的冰点温度更有用,结果是在华氏温标中水的冰点温度为32度,沸腾温度为212度,两点之间相差180度。

摄氏或百分温标在科学研究中更为常用,将纯水冰点设为0度,沸点设为100度更有意义。注意这样在冰点和沸点之间正好是100度,这也意味着在摄氏温标中改变一度比华氏温标中需要更多的能量。

第三种温标是开氏温标。它和摄氏温标用一样的尺度,只不过是基于绝对零度。绝对零度就是所有原子停止运动的理论温度,该值为-273度。在开氏温标中,水在273度结冰,在373度沸腾。

密度,比重和蒸汽密度

物质的一个重要性质就是密度(dense)。当我们说某个东西是密集的,我们指的是单位体积的数量或重量。软木塞就比等积的铁密度低。密度以每立方厘米材料重量即克来衡量。水作为标准(在4摄氏度)每立方厘米重1克。其它的物质的密度用和相当体积的水的比值来表示。硅的密度为2.3,这样每立方厘米的硅就重2.3克。

比重(specific gravity)这个术语指的是4摄氏度时液体和气体的密度,它是物质的密度与水的比值。汽油的比重为0.75,意味着是水密度的75%。

蒸汽密度(vapor density)是指在一定温度和压力下气体的密度。空气每一立方厘米的密度为1,可以作为参考值。氢气的蒸汽密度为0.60,它是同体积的空气密度的60%。在同样大小的容器中,氢气的重量会是空气的60%。

压力和真空

物质另一个重要方面就是压力。压力作为一种性质通常用于液体和气体。压力定义为施加在容器表面上单位面积的力。 气缸中的气压迫使气体进入工艺反应室。所有的工艺机器都用量表表来测量和控制气压。

气压表示为英镑每平方英寸(psia),大气压或托。一个大气压就是在特定温度下包围地球的大气压力。这样高压氧化系统在5个大气压下工作,其压力是大气压的5倍。

空气的大气压为14.7psia,在气缸中气压要用psig或英镑每平方英寸的表。这意味着表的读数是绝对的,它并不包括外界的大气压。

真空(vacuum)也是在半导体工艺中要遇到的术语和情况,它实际上是低压的情况。一般来说,压力低于标准大气压就认为是真空。真空条件是用压力单位来衡量的。

低压倾向于用托来表示。这个单位是以意大利科学家托里切利,他在气体和其性质领域做出了很多重要发现。1托就是压力计中一毫米汞柱(manometer)所对应的压力。

如图2.18a所示的,想象当压力超过大气压时对压力计中水银柱的影响。当压力升高,在盘子里的水银受压而使水银柱升高。现在想象当气体从系统中抽走形成真空时会怎样(图2.18b)。只要有任何气体分子或原子在压力计中,施加在盘中的水银上的压力就会很小,从而水银柱就会升高一点点但很有限。水银柱变化是毫米级的,是与压力相关,或者在这种情况下是与真空有关。

蒸发,溅射和离子都工作在10-6到10-9托的真空(压力)。如果将其转换为只有一个简单压力计的真空系统,这就意味着水银柱才0.000000001(1x10-9)到0.000001(1x10-6)毫米高,非常小的长度。在实践中,水银压力计是不能测量这么低的压力的,而是使用其它更灵敏的压力表。

#1 第二章 半导体材料和工艺化学品---5

第二章 半导体材料和工艺化学品---5

酸,碱和溶剂

酸和碱

半导体工艺需要大量化学液体来刻蚀、清洗和冲洗晶圆和其它部件。化学家们把这些化学品分为三大类:7

**酸

**碱

**溶剂

酸和碱的不同之处在于液体中离子的不同。酸中含有氢离子(hydrogen ions),而碱含有氢氧离子(hydroxide ions)。对水分子的研究解释了不同之处。

水的化学式一般写成H2O,它也可写成HOH。将其分解,我们发现水是由带正电的氢离子(H+)和带负电的氢氧离子(OH-)。

当水与其它元素混合,要么是氢离子,要么就氢氧离子与其它物质结合(图2.19)。含有氢离子的液体叫做酸,含有氢氧离子的叫做碱。通常在家中就可找到酸和碱:柠檬汁和醋是酸,氨水和溶于水的苏打是碱。

酸、碱

图2.19 酸碱溶液

酸进一步可分为两类:有机的和无机的。有机酸含有碳氢化合物而无机酸没有。磺酸是有机酸,氢氟酸是无机酸。

酸和碱的强度和反应用pH值来衡量。该值从0到14,7为中性点。水既不是酸又不是碱,所以其pH值为7。强酸如硫酸(H2SO4)pH值较低为0到3,强碱如氢氧化钠(NaOH)pH值比7要高。

酸和碱都会与皮肤和其它化学品发生反应,必须按规定的安全规程来存储和操作。

溶剂

溶剂是不带电的,pH值为中性。水就是溶剂,实际上它溶解其它物质的能力最强。在晶圆工艺中也经常应用酒精和丙酮。

晶圆工艺中大多数溶剂是易挥发易燃的。要在通风良好的地方使用,要按照规定规程来存储和使用,这是非常重要的。

安全问题

在半导体工艺区域存在着化学品存储、使用和处理的危险,电的危险和其它危险。公司应通过培训和安全检查来提高员工的知识、技能和认识。

从左到右依次为:硫酸、柠檬汁、橙汁、干酪、奶、纯水、蛋清、硼砂、镁乳、冲影液、石灰、氢氧化钠

酸性增强、碱性增强(碱性、腐蚀性)

图2.20 pH测量系统

安全材料数据表

对于带入生产工厂的任何化学品,供应商必须提供一份材料安全数据表(MSDS)。这是(美国:译者注)联邦职业、安全和健康法案(OSHA)的规定。这个表也叫做OSHA表20,该表包含着化学品相关的存储、健康、第一救援和使用信息。根据现行规定,在工厂MSDS表必须填写并且员工可以获取。

关键术语和概念

酸、碱、溶剂 空穴

玻尔原子模型 第三、五族化合物

载流子迁移率 离子

导电率/电阻率 安全材料数据表

导体 N型和P型

绝缘体 元素周期表

掺杂剂 pH值表

掺杂半导体 压力和真空

电子、质子、中子 硅/锗

元素 固体、液体、气体

铁电材料 温度计

砷化镓

复习问题

1.描述导体、绝缘体和半导体之间的电性差异。

2.为什么固态器件需要掺杂半导体?

3.金属和本征半导体,哪一个电阻率更高?

4.给出两个理由解释为什么硅是最常用的半导体材料。

5.给出一种能够做N型硅的元素。

6.一个P型半导体表现出_______(负电或正电)流。

7.在下面的描述中选择酸、碱和溶液的分类方法。

a. 包含OH-离子 b. 包含H+离子

c. pH值呈中性

8.酸的pH值从_______到_______。

9.碱的pH值从_______到_______。

10.水的pH值是多少?

参考文献

4.1 Fujitsu Quantum Devices Limited, website.

4.2 R. E. Williams, Gallium Arsenide Processing Techniques, Artech House, Inc., Dedham, MA, 1984.

4.3 “Industry News,” Semiconductor International, March 1994, p.22.

4.4 W. Conrad Holton, Silicon Germanium: Finally for Real, Solid State Electronics, November 1997, p. 119.

4.5 Robert E. Jones, “Integration of Ferroelectrics into Nonvolitile Memories,” Solid State Technology, October 1997, p. 201.

4.6 R. Allen et al., “MNST Wafer Cleaning,” Solid State Technology, January 1994, p. 61.

第三章 晶圆制备---1

概述

在这一章里,讲述了沙子转变成晶体及晶圆和用于芯片制造级的抛光片的生产步骤。

目的

完成本章后您将能够:

1,解释晶体和非晶体的区别。

2,解释多晶和单晶的区别。

3,画出两种在半导体工序重要的晶圆晶向示意图。

4,解释晶体生长直拉法,区溶法,液晶压缩直拉法。

5,画出晶圆制备工艺的流程示意图。

6,解释晶圆上参考面或缺口的使用和意义。

7,描述圆边晶圆在芯片制造工艺中的好处。

8,描述平整和无损伤晶圆在芯片制造工艺中的好处。

介绍

高密度和大尺寸芯片的发展需要大直径的晶圆。在上世纪60年代开始使用的是1²直径的晶圆,而现在业界根据90年代的工艺要求生产200毫米直径的晶圆。300 毫米直径的晶圆也已经投入生产线了,而根据SIA的技术路线图,到2007年,300毫米将成为标准尺寸。以后预期会是400毫米或450毫米直径的晶圆。大直径的晶圆是由不断降低芯片成本的要求驱动的。然而,这对晶圆制备的挑战是巨大的。大直径意味着高重量,这就需要更多坚固的工艺设备。在晶体生长中,晶体结构上和电学性能一致性及污染的问题是一个挑战,这些挑战和几乎每一个参数更紧的工艺规格要求共存。与挑战并进和提供更大直径晶圆是芯片制造不断进步的关键。

半导体硅制备

半导体器件和电路在半导体材料晶圆的表层形成,半导体材料通常是硅。这些晶圆的杂质含量水平必须非常低,必须掺杂到指定的电阻率水平,必须是指定的晶体结构,必须是光学的平面,并达到许多机械及清洁度的规格要求。制造IC级的硅晶圆分四个阶段进行:

晶圆制备阶段

**矿石到高纯气体的转变

**气体到多晶的转变

**多晶到单晶,掺杂晶棒的转变

**晶棒到晶圆的制备

半导体制造的第一个阶段是从泥土里选取和提纯半导体材料的原料。提纯从化学反应开始。对于硅,化学反应是从矿石到硅化物气体,例如四氯化硅或三氯硅烷。杂质,例如其他金属,留在矿石残渣里。硅化物再和氢反应(图3.1)生成半导体级的硅。这样的硅的纯度达99.9999999%,是地球上最纯的物质之一。1它有一种称为多晶或多晶硅(polysilicon)的晶体结构。

晶体材料

材料中原子的组织结构是导致材料不同的一种方式。有些材料,例如硅和锗,原子在整个材料里重复排列成非常固定的结构,这种材料称为晶体(crystals)。

原子没有固定的周期性排列的材料称为非晶或无定形(amorphous)。塑料是无定形材料的例子。

晶胞

对于晶体材料实际上可能有两个级别的原子组织结构。第一个是单个原子的组织结构。晶体里的原子排列在称为晶胞(unit cell)的结构的特定点。晶胞是晶体结构的第一个级别。晶胞结构在晶体里到处重复。

另一个涉及晶胞结构的术语是晶格(lattice)。晶体材料具有特定的晶格结构,并且原子位于晶格结构的特定点。

在晶胞里原子的数量、相对位置及原子间的结合能会引发材料的许多特性。每个晶体材料具有独一无二的晶胞。硅晶胞具有16个原子排列成金刚石结构(图3.2)。砷化镓晶体具有18个原子的晶胞结构称为闪锌矿结构(图3.3)。

多晶和单晶

晶体结构的第二个级别和晶胞的构成有关。在本征半导体中,晶胞间不是规则的排列。这种情形和方糖杂乱无章的堆起来相似,每个方糖代表一个晶胞。这样排列的材料具有多晶结构。

当晶胞间整洁而有规则的排列时第二个级别的结构发生了(图3.4)。那样排列的材料具有单晶结构。

单晶材料比多晶材料具有更一致和更可预测的特性。单晶结构允许在半导体里一致和可预测的电子流动。在晶圆制造工艺的结尾,晶体的一致性对于分割晶圆成无粗糙边缘的晶元是至关重要的(见18章)。

晶体定向

对于一个晶圆,除了要有单晶结构之外,还需要有特定的晶向(crystal orientation)。通过切割如图3.4的单晶块可以想象这个概念。在垂直平面上切割将会暴露一组平面,而角对角切割将会暴露一个不同的平面。每个平面是独一无二的,不同在于原子数和原子间的结合能。每个平面具有不同的化学、电学和物理特性,这些特性将赋予晶圆。晶圆要求特定的晶体定向。

晶面通过一系列称为密勒指数的三个数字组合来表示。如图3.5有两个简单的立方晶胞嵌套在XYZ坐标中。两个在硅晶圆中最通常使用的晶向是<100>和<111>晶面。晶向描述成1-0-0面 和1-1-1面,括弧表示这三个数是密勒指数。

<100>晶向的晶圆用来制造MOS器件和电路,而<111>晶向的晶圆用来制造双极型器件和电路。砷化镓晶体只能沿<100>晶面切割。

注意在图3.6<100>晶面有一个正方形,而<111>晶面有一个三角形。当晶圆破碎时这些定向会如图3.6展现出来。<100>晶向的晶圆碎成四方形或正好90度角破裂。<111>晶向的晶圆碎成三角形。

晶体生长

半导体晶圆是从大块半导体材料切割而来的。那些半导体材料,或叫做晶棒,是从大块的具有多晶结构和未掺杂本征材料生长得来的。把多晶块转变成一个大单晶,给予正确的定向和适量的N型或P型掺杂,叫做晶体生长。

使用三种不同的方法来生长单晶:直拉法、液体掩盖直拉法、区溶法。

直拉法(CZ)

大部分的单晶是通过直拉法生长的(图3.7)。设备有一个石英坩埚,由负载高频波的环绕线圈来加热,或由电流加热器来加热。坩埚装载半导体材料多晶块和少量掺杂物。选择掺杂材料来产生N型或P型材料。开始在1415°C把多晶和搀杂物加热到液体状态,接下来籽晶安置到刚接触到液面(叫做熔融物)。籽晶是具有和所需晶体相同晶向的小晶体,籽晶可由化学气相的技术制造。在实际应用中,它们是一片片以前生长的单晶并重复使用。

当籽晶从熔融物中慢慢上升时,晶体生长开始了。籽晶和熔融物间的表面张力致使一层熔融物的薄膜附着到籽晶上然后冷却。在冷却过程中,在熔化的半导体材料的原子定向到籽晶一样的晶体结构。实际结果是籽晶的定向在生长的晶体中传播。在熔融物中的搀杂原子进入生长的晶体中,生成N型或P型晶体。

为了实现均匀掺杂、完美晶体和直径控制,籽晶和坩埚(伴随着拉速)在整个晶体生长过程中是以相反的方向旋转的。工艺控制需要一套复杂的反馈系统,综合转速、拉速及熔融物温度参数。

拉晶分三段,开始放肩形成一薄层头部,接着是等径生长,最后是收尾。直拉法能够生成几英尺长和直径大到十二英寸或更多的晶体。200毫米晶圆的晶体将会重达450磅,需要花费三天时间生长。

液体掩盖直拉法(LEC)

液体掩盖直拉法2用来生长砷化镓晶体。实质上它和标准的直拉法(CZ)一样,但为砷化镓做了重要改进。由于熔融物里砷的挥发性,改进是必须的。在晶体生长的温度条件下,镓和砷起反应,砷会挥发出来造成不均匀的晶体。

对这个问题有两个解决办法。一个是给单晶炉加压来抑制砷的挥发,另一个是液体掩盖直拉法工艺(图3.9)。液体掩盖直拉法使用一层氧化硼(B2O3)漂浮在熔融物上面来抑制砷的挥发。在这个方法中,单晶炉里需要大约一个大气压。

区熔法

区熔法晶体生长2是在本文中介绍的技术历史上早期发展起来的几种工艺之一,仍然在特殊需要中使用。直拉法的一个缺点是坩埚中的氧进入到晶体中,对于有些器件,高水平的氧是不能接受的。对于这些特殊情况,晶体必须用区熔法技术来生长以获得低氧含量晶体。

区熔法晶体生长(图3.10)需要一根多晶棒和浇铸在模子里的掺杂物。籽晶熔合到棒的一端。夹持器装在单晶炉里。当高频线圈加热多晶棒和籽晶的界面时,多晶到单晶的转变开始了。线圈沿着多晶棒的轴移动,一点点把多晶棒加热到液相点。在每一个熔化的区域,原子排列成末端籽晶的方向。这样整个棒以开始籽晶的定向转变成一个单晶。

区熔法晶体生长不能够象直拉法那样生长大直径的单晶,并且晶体有较高的位错密度,但不需用石英坩埚会生长出低氧含量的高纯晶体。低氧晶体可以使用在高功率的晶闸管和整流器。这两种方法比较如图3.11。

第三章 晶圆制备--2

晶体和晶圆质量

半导体器件需要高度的晶体完美。但是即使使用了最成熟的技术,完美的晶体还是得不到的。不完美,叫做晶体缺陷,会产生不平均的二氧化硅膜生长、差的外延膜的淀积、晶圆里不均匀的掺杂层及其它问题而导致工艺问题。在完成的器件中,晶体缺陷会引起有害的电流漏出,可能阻止器件在正常电压下工作。有三类重要的晶体缺陷:

1. 点缺陷

2. 位错

3. 原生缺陷

点缺陷

点缺陷的来源有两类。一类来源是由晶体里杂质原子挤压晶体结构引起应力所致;第二类来源称为空位,在这种情况下,有某个原子在晶体结构的位置上缺失了。

空位是一种发生在每一个晶体里的自然现象。不幸的是空位无论在晶体或晶圆加热和冷却都会发生,例如在制造工艺过程中。减少空位是低温工艺背后的一个推动力。

位错

位错是在单晶里一组晶胞排错位置。这可以想象成在一堆整齐排列的方糖中有一个排列和其它的发生了微小的偏差。

位错在晶圆里的发生由于晶体生长条件和晶体里晶格应力,也会由于制造过程中的物理损坏。碎片或崩边成为晶格应力点会,产生一条位错线,随着后面的高温工艺扩展到晶圆内部。位错能通过表面一种特殊的腐蚀显示出来。典型的晶圆具有每平方厘米200到1000的位错密度。

腐蚀出的位错出现在晶圆的表面上,形状代表了它们的晶向。<111>的晶圆腐蚀出三角形的位错,<100>的晶圆出现方形的腐蚀坑(图3.6)。

原生缺陷

在晶体

晶体准备

截断

晶体从单晶炉里出来以后,到最终的晶圆会经历一系列的步骤。第一部是用锯子截掉头尾。

直径滚磨

在晶体生长过程中,整个晶体长度中直径有偏差(图3.14)。晶圆制造过程有各种各样的晶圆固定器和自动设备,需要严格的直径控制以减少晶圆翘曲和破碎。

直径滚磨是在一个无中心的滚磨机上进行的机械操作。机器滚磨晶体到合适的直径,无需用一个固定的中心点夹持晶体在车床型的滚磨机上。

晶体定向,电导率和电阻率检查

在晶体提交到下一步晶体准备前,必须要确定晶体是否达到定向和电阻率的规格要求。

晶体定向(图3.15)是由X射线衍射或平行光衍射来确定的。在两种方法中,晶体的一端都要被腐蚀或抛光以去除损伤层。下一步晶体被安放在衍射仪上,X射线或平行光反射晶体表面到成像板(X射线)或成像屏(平行光)。在成像板或成像屏上的图案显示晶体的晶面(晶向)。在图3.15显示的图案代表<100>晶向。

许多晶体生长时有意偏离重要的<100>和<100>晶面一点角度。这些偏晶向在晶圆制造过程中会带来很多好处,特别是在离子注入工艺中,原因会在工艺应用章中涉及到。

晶棒粘放在一个切割块上来保证晶圆从晶体正确的晶向切割。

由于晶体是经过掺杂的,一个重要的电学性能检查是导电类型(N或P)来保证使用了正确的掺杂物。热点探测仪连接到极性仪用来在晶体中产生空穴或电子(和类型相关),在极性仪上显示导电类型。

进入晶体的掺杂物的数量由电阻率测量来确定,使用四探针仪。见13章此测量技术的描述。在第2章(图2.7)讲到的曲线表示了电阻率和N型P型硅掺杂含量的关系。

由于在晶体生长工艺中掺杂量的变异,电阻率要延着晶体的轴向测量。这种变异导致晶圆进入几个电阻率规格范围。在后面的工序,晶圆将根据电阻率范围分组来达到客户的规格要求。

滚磨定向指示

一旦晶体在切割块上定好晶向,就沿着轴滚磨出一个参考面(图3.16)。这个参考面将会在每个晶圆上出现,叫做主参考面。参考面的位置延着一个重要的晶面,这是通过晶体定向检查来确定的。

在制造工艺中,参考面对晶向起可见的参考作用。它用来放置第一步的光刻图案掩膜版,所以芯片的晶向总是沿着一个重要的晶面。

在许多晶体中,在边缘有第二个较小的参考面。第二个参考面对于主参考面的位置是一种代码,它不仅用来区别晶圆晶向而且区别导电类型。这种代码在图3.17中显示。

对于大直径的晶圆,在晶体上滚磨出一个缺口来指示晶向。

切片

用有金刚石涂层的内圆刀片把晶圆从晶体上切下来(图3.18)。这些刀片是中心有圆孔的薄圆钢片。圆孔的内缘是切割边缘,用金刚石涂层。内圆刀片有硬度,但不用非常厚。这些因素减少刀口(切割宽度)尺寸,也就减少一定数量的晶体被切割工艺所浪费。

对于300毫米直径的晶圆,使用线切割来保证小锥度的平整表面和最少量的刀口损失。

第三章 晶圆制备--3

晶圆刻号

大面积的晶圆代在晶圆制造工艺中有高价值,区别它们是防止误操作所必需的,并且可以保持精确的可追溯性。使用条形码和数字矩阵码(图3.19)的激光刻号被采用了。3对300毫米的晶圆,激光点是一致认同的方法。

磨片

半导体晶圆的表面要规则,且没有切割损伤,并要完全平整。第一个要求来自于很小尺度的制造器件的表面和次表面层。它们的尺度在0.5到2微米之间。为了获得半导体器件相对尺寸的概念,想象图3.20的剖面和房子一样高,大概8英尺,在那个范围内,在晶圆的工作层都存在顶部一到二英寸或更小的区域。

平整度是小尺寸图案是绝对的必要条件(见11章)。先进的光刻工艺把所需的图案投影到晶圆表面,如果表面不平,投影将会扭曲就象电影图像在不平的银幕上没法聚焦一样。

平整和抛光的工艺分两步:磨片和化学机械抛光(图3.21)。磨片是一个传统的磨料研磨工艺,精调到半导体使用要求。磨片的主要目的是去除切片工艺残留的表面损伤。

化学机械抛光(CMP)

最终的抛光步骤是一个化学腐蚀和机械磨擦的结合。晶圆装在旋转的抛光头上,下降到抛光垫的表面以相反的方向旋转。抛光垫材料通常是有填充物的聚亚安酯铸件切片或聚氨酯涂层的无纺布。二氧化硅抛光液悬浮在适度的含氢氧化钾或氨水的腐蚀液中,滴到抛光垫上。

碱性抛光液在晶圆表面生成一薄层二氧化硅。抛光垫机以持续的机械磨擦作用去除氧化物,晶圆表面的高点被去除掉,直到获得特别平整的表面。如果一个半导体晶圆的表面扩大到10000英尺(飞机场跑道的长度),在总长度中将会有正负2英寸的平整度偏差。

获得极好平整度需要规格和控制抛光时间、晶圆和抛光垫上的压力、旋转速度、抛光液颗粒尺寸、抛光液流速、抛光液的PH值、抛光垫材料和条件。

化学机械抛光是业界发展起来的制造大直径晶圆的技术之一。在晶圆制造工艺中,新层的建立会产生不平的表面,使用CMP以平整晶体表面。在这个应用中,CMP被翻译成化学机械平面化(Planarization)。具体CMP使用的解释在12章。

背处理

在许多情况下,只是晶圆的正面经过充分的化学机械抛光。背面留下从粗糙或腐蚀到光亮的外观。对于某些器件的使用,背面可能会受到特殊的处理导致晶体缺陷,叫做背损伤。背损伤产生位错的生长辐射进入晶圆,这些位错起象是陷阱,俘获在制造工艺中引入的可移动金属离子污染。这个俘获现象又叫做吸杂(图3.22)。背面喷沙是一种标准的技术,其它的方法包括背面多晶层或氮化硅的淀积。

双面抛光

对大直径晶圆许多要求之一是平整和平行的表面。许多300毫米晶圆的制造采用了双面抛光,以获得局部平整度在25´25毫米测量面时小于0.25微米到0.18微米的规格要求。4缺点是在后面的工序中必须使用不划伤和不污染背面的操作技术。

边缘倒角和抛光

边缘倒角是使晶圆边缘圆滑的机械工艺(图3.23)。应用化学抛光进一步加工边缘,尽可能的减少制造中的边缘崩边和损伤,边缘崩边和损伤能导致碎片或是成为位错线的核心。

晶圆评估

在包装以前,需要根据用户指定的一些参数对晶圆(或样品)进行检查。图3.24列举了一个典型的规格要求。

主要的考虑是表面问题如颗粒,污染和雾。这些问题能够用强光或自动检查设备来检测出。

氧化

晶圆在发货到客户之前可以进行氧化。氧化层用以保护晶圆表面,防止在运输过程中的划伤和污染。许多公司从氧化开始晶圆制造工艺,购买有氧化层的晶圆就节省了一个生产步骤。氧化工艺在第7章解释。

包装

虽然花费了许多努力生产高质量和洁净的晶圆,但从包装方法本身来说,在运输到客户的过程中,这些品质会丧失或变差。所以,对洁净的和保护性的包装有非常严格的要求。包装材料是无静电、不产生颗粒的材料,并且设备和操作工要接地,放掉吸引小颗粒的静电。晶圆包装要在洁净室里进行。

晶圆外延

尽管起始晶圆的质量很高,但对于形成互补金属氧化物半导体(CMOS)器件而言还是不够的,这些器件需要一层外延层。许多大晶圆供应商有能力在供货前对晶圆外延。此器件技术在16章中讨论。

关键术语和概念

晶体 籽晶

晶胞 熔融物

多晶 晶体生长

单晶 直拉法

晶体定向 区熔法

<100>晶面 液体掩盖直拉法

<111>晶面 晶圆参考面

点缺陷 晶圆参考面代码

晶体位错 化学机械抛光

原生缺陷 背损伤

边缘倒角 切片

滑移 空位

复习问题

1. 在多晶结构里原子不是有序排列的(对/错)。

1. 在单晶结构里晶胞不是有序排列的(对/错)。

2. 画一个晶胞立方并指出<100>晶面。

3. <111>晶向的晶圆是用来做------(双极型,MOS)器件。

4. 如果籽晶是<100>晶向,拉出的晶体是什么晶向?

5. 画一个直拉晶体生长的示意图并指出所有重要的部分。

6. 在晶体生长过程中,熔融物材料从单晶结构改变到多晶结构(对/错)。

7. 为什么晶圆的边缘是圆的?

8. 画一个晶圆准备的流程图。

9. 给出两个原因,为什么半导体晶圆需要平整的表面?

参考文献

3.1 Sumitomo Sitix Product Brochure.

3.2 R. E. Williams, Gallium Arsenide Processing Techniques, Artech House Inc., Dedham MA, 1984, p. 37.

3.3 S. J. Brunkhorst, and D. W. Sloat, “The impact of the 300-mm transition on silicon wafer suppliers,” Solid state Technology, January 1998, p.87.

3.4 Ibid.

第四章 芯片制造概述--1

概述

本章将介绍基本芯片生产工艺的概况。本章通过在器件表面产生电路元件的工艺顺序来阐述四种最基本的平面制造工艺。接下来解释了从功能设计图到光刻掩膜板的生产的电路设计过程。最后, 详细描述了晶圆和器件的特性和术语。

目的

完成本章后您将能够:

1. 鉴别和解释最基本的四种晶圆生产工艺。

2. 辨别晶圆的各个部分。

3. 描绘集成电路设计的流程图。

4. 说出集成电路合成布局图和掩膜组的定义与用途。

5. 画出作为基础工艺之一的掺杂工艺顺序截面图。

6. 画出作为基础工艺之一的金属化工艺顺序的截面图。

7. 画出作为基础工艺之一的钝化层工艺顺序的截面图。

8. 识别集成电路电路器件的各个部分。

晶圆生产的目标

芯片的制造,分为四个阶段:原料制作、单晶生长和晶圆的制造、集成电路晶圆的生产、集成电路的封装。前两个阶段已经在本书的第三章涉及。本章讲述的是第三个阶段,集成电路晶圆生产的基础知识。

集成电路晶圆生产(wafer fabrication)是在晶圆表面上和表面内制造出半导体器件的一系列生产过程。整个制造过程从硅单晶抛光片开始,到晶圆上包含了数以百计的集成电路芯片(图4.1)。

晶圆术语

图4.2列举了一片成品晶圆。接下来将向读者讲解晶圆表面各部分的名称:

图4.2 晶圆术语

1. 器件或叫芯片(Chip, die, device, microchip, bar): 这个名词指的是在晶圆表面占大部分面积的微芯片掩膜。

2. 街区或锯切线(Scribe lines, saw lines, streets, avenues):在晶圆上用来分隔不同芯片之间的街区。街区通常是空白的, 但有些公司在街区内放置对准靶, 或测试的结构(见 ‘ Photomasking’ 一章)。

3. 工程试验芯片(Engineering die, test die):这些芯片与正式器件(或称电路芯片)不同。它包括特殊的器件和电路模块用于对晶圆生产工艺的电性测试。

4. 边缘芯片( Edge die):在晶圆的边缘上的一些掩膜残缺不全的芯片而产生面积损耗。由于单个芯片尺寸增大而造成的更多边缘浪费会由采用更大直径晶圆所弥补。推动半导体工业向更大直径晶圆发展的动力之一就是为了减少边缘芯片所占的面积。

5. 晶园的晶面( Wafer Crystal Plans):图中的剖面标示了器件下面的晶格构造。此图中显示的器件边缘与晶格构造的方向是确定的。

6. 晶圆切面/凹槽( Wafer flats/notches):例如图示的晶圆有主切面和副切面,表示这是一个P型<100>晶向的晶圆(见第三章的切面代码)。300 毫米晶圆都是用凹槽作为晶格导向的标识。

晶圆生产的基础工艺

集成电路芯片有成千上百的种类和功用。然而,它们都是由为数不多的基本结构(主要为双极结构和金属氧化物半导体结构,见第十六章)和生产工艺制造出来的。类似于汽车工业,这个工业生产的产品范围很广,从轿车到推土机。然而,金属成型、焊接、油漆等工艺是对有的汽车厂都是通用的。在汽车厂内部,这些基本的工艺以不同的方式被应用,来制造出客户希望的产品。

同样,芯片制造也是一样。制造企业使用四种最基本的工艺方法通过大量的工艺顺序和工艺变化制造出特定的芯片。这些基本的工艺方法是增层、光刻、掺杂、热处理(图4.3)。

增层

增层是在晶圆表面形成薄膜的加工工艺。分析图4.4的简单MOS晶体管可看出在晶圆表面生成了许多的薄膜。这些薄膜可以是绝缘体、半导体或导体。它们是由不同的材料组成,使用多种工艺生长或淀积的。

这些主要的工艺技术是生长二氧化硅膜和淀积不同种材料的薄膜。通用的淀积技术是化学汽相淀积(CVD) 、蒸发和溅射。图4.6列出了常见的薄膜材料和增层工艺。其中每项的具体情况在本书的工艺章节各有阐述。各种薄膜在器件结构内的功用在第16章进行解释。

层别(Layers) 热氧化工艺(Thermal Oxidation) 化学汽相淀积工艺(Chemical Vapor Deposition) 蒸发工艺 (Evaporation) 溅射工艺(Sputtering)

绝缘层 (Insulators) 二氧化硅(Silicon Deioxide) 二氧化硅(Silicon Dioxide) 氮化硅(Silicon Nitrides) 二氧化硅 (Silicon Dioxide) 一氧化硅(Silicon Monoxide)

半导体层 (semiconductors) 外延单晶硅 (Epitaxial Silicon) 多晶硅 (Poly Silicon)

导体层 (conductors) 铝 (Aluminum) 铝/硅合金(Aluminum/Silicon) 铝铜合金 (Aluminum/Copper) 镍铬铁合金 (Nichrome) 黄金 (Gold) 钨 (Tungsten) 钛 (Titanium) 钼 (molybdenum) 铝/硅合金(Aluminum/Silicon) 铝铜合金 (Aluminum/Copper)

图 4.6 薄层分类/工艺与材料的对照表

光刻

光刻是通过一系列生产步骤将晶圆表面薄膜的特定部分除去的工艺(图4.7)。在此之后,晶圆表面会留下带有微图形结构的薄膜。被除去的部分可能形状是薄膜内的孔或是残留的岛状部分。

光刻工艺也被称为大家熟知的Photomasking, masking, photolithography, 或microlithography。在晶圆的制造过程中,晶体三极管、二极管、电容、电阻和金属层的各种物理部件在晶圆表面或表层内构成。这些部件是每次在一个掩膜层上生成的,并且结合生成薄膜及去除特定部分,通过光刻工艺过程,最终在晶圆上保留特征图形的部分。光刻生产的目标是根据电路设计的要求,生成尺寸精确的特征图形,并且在晶圆表面的位置正确且与其它部件(parts)的关联正确。

光刻是所有四个基本工艺中最关键的。光刻确定了器件的关键尺寸。光刻过程中的错误可造成图形歪曲或套准不好,最终可转化为对器件的电特性产生影响。图形的错位也会导致类似的不良结果。光刻工艺中的另一个问题是缺陷。光刻是高科技版本的照相术,只不过是在难以置信的微小尺寸下完成。在制程中的污染物会造成缺陷。事实上由于光刻在晶圆生产过程中要完成5层至20层或更多,所以污染问题将会放大。

第四章 芯片制造概述--2

掺杂

掺杂是将特定量的杂质通过薄膜开口引入晶圆表层的工艺制程(图4.8)。它有两种工艺方法:热扩散(thermal diffusion)和离子注入(implantation),都在第十一章有详细阐述。

热扩散是在1000摄氏度左右的高温下发生的化学反应,晶圆暴露在一定掺杂元素汽态下。扩散的简单例子就如同除臭剂从压力容器内释放到房间内。汽态下的掺杂原子通过扩散化学反应迁移到暴露的晶圆表面,形成一层薄膜。在芯片应用中,热扩散也被称为固态扩散,因为晶圆材料是固态的。热扩散是一个化学反应过程。

离子注入是一个物理反应过程。晶圆被放在离子注入机的一端,掺杂离子源(通常为气态)在另一端。在离子源一端,掺杂体原子被离化(带有一定的电荷),被电场加到超高速,穿过晶圆表层。原子的动量将掺杂原子注入晶圆表层,好象一粒子弹从枪内射入墙中。

掺杂工艺的目的是在晶圆表层内建立兜形区, 或是富含中子(N型)或是富含空穴(P型)。这些兜形区形成电性活跃区和PN结,在电路中的晶体管、二极管、电容器、电阻器都依靠它来工作。

热处理

热处理是简单地将晶圆加热和冷却来达到特定结果的制程。在热处理的过程中,在晶圆上没有增加或减去任何物质,另外会有一些污染物和水汽从晶圆上蒸发。

在离子注入制程后会有一步重要的热处理。掺杂原子的注入所造成的晶圆损伤会被热处理修复,称为退火,温度在1000摄氏度。另外,金属导线在晶圆上制成后会有一步热处理。这些导线在电路的各个器件之间承载电流。为了确保良好的导电性,金属会在450摄氏度热处理后与晶圆表面紧密熔合。热处理的第三种用途是通过加热在晶圆表面的光刻胶将溶剂蒸发掉,从而得到精确的图形。

制造半导体器件和电路

当今的芯片结构含有多层薄膜和掺杂,很多层的薄膜生长或淀积在晶圆表面,包括多层的导体配合以绝缘体(图4.10四层截面)。完成如此复杂的结构需要很多生产工艺。并且每种工艺按照特定顺序进行包含一些工步和和子工步。64G CMOS 器件的特殊制程需要180个重要工艺步骤,52次清洗,和多达28层膜版。1尽管如此,所有这些工艺步骤都是四大基础工艺之一。图4.11列出了基础工艺和每一个工艺方案的原理。在图中的是一个简单器件-MOS栅极硅晶体管的构成,插图说明了制造的顺序。这类晶体管各部分的功能和晶体管的工作原理在第十四章有详细阐述。

Basic Operation 基本工艺 Process 制程方法 Options 具体分类

Layering 增层 Oxidation 氧化 Atmospheric 常压氧化法

High Pressure 高压氧化法

Rapid Thermal Oxidation 快速热氧化

Chemical Vapor Deposition 化学汽相淀积 Atmospheric Pressure 常压化学汽相淀积

Low Pressure (LPCVD) 低压化学汽相淀积

Plasma Enhanced (PECVD)等离子增强化学汽相淀积

Vapor Phase Epitaxy (VPE) 汽相外延法

Metaloranic CVD (MOCVD) 金属有机物CVD

Moleculur Beam Epitaxy(MBE)分子束外延

Physical Vapor Deposition(PCD) 物理汽相淀积 Vacuum Evaporation 真空蒸发法

Sputtering 溅射法

Patterning 光刻 Resist 光刻胶 Positive 正胶工艺

Negative 负胶工艺

Exposure Systems 暴光系统 Contact 接触式暴光

Proximity 接近式暴光

Scanning Projection 投影式暴光

Stepper 步进暴光机

Exposure Sources 暴光源 High Pressure Mercury 高压汞

X-rays X射线

E-Beams 电子束暴光

Imaging Processes 成象工艺 Single Layer Resist 单层光刻胶

Multilayer Resist 多层光刻胶

Antireflecting Layers 防反射层

Off-Axis Illumination 偏轴照明

Planarization 平坦化

Contrast Enhancement 对比度提高

Etch 刻蚀 Wet Chemistry-Liqiud/vapor 湿化学刻蚀

Dry(Plasma) 干法刻蚀

Lift-Off 剥脱

Ion Millling 离子磨

Reaction Ion Etch(RIE) 反应离子刻蚀法

Doping 掺杂 Diffusion 扩散 Open Tube-Horizontal/Vertical (开放式炉管-水平/竖置)

Closed Tube 封闭炉管

Rapid Thermal Process(RTP) 快速热处理

Ion Implantation Medium/High Current 中/高电流离子注入

Low/High Voltage(energy) 低能量/高能量离子注入

Heating热处理 Thermal加热 Hot Plates 加热盘

Convection 热对流

RTP 快速加热

Radiation热辐射 Infrared (IR)红外线加热

图4.11 晶圆制造加工/工艺的一览表

电路设计

电路设计是产生芯片整个过程的第一步。电路设计由布局和尺寸。设计电路上一块块的功能电路图开始,比如逻辑功能图(见图4.12)。这个逻辑图设计了电路要求的主要功能和运算。接下来,设计人员将功能逻辑图转化为示意图(图4.13)。示意图标示出了各种电路元件的数量和连接关系。每一个元件在图上由符号代表。附在示意图后的是电路运行必需的电性参数(电路、电压、电阻,等等)。

第三步是电路版面设计,它是半导体集成电路所独有的。电路的工作运行与很多因素相关,它包括材料电阻率,材料物理特性和元件的物理尺寸。另外的因素是各个元件之间的相对定位关系。所有这些考虑因素决定了元件、器件、电路的物理布局和尺寸。线路图设计开始于使用复杂尖端的的计算机辅助设计系统(CAD)将每一个电路元件转为具体的图形和尺寸。通过CAD系统构构造成电路,接下来将是把最后设计完全地复制。得出的结果是一张展示所有子层图形的复合叠加图。此图称为复合图(composite)。复合图类似于一座多层办公楼的设计图,从顶部俯视并展示所有楼层。但是,复合图是实际电路尺寸的许多倍。

制造集成电路和盖楼房同样需要一层层地建,因此必须将电路的复合图分解为每层的设计图。图4.14以一个简单的金属氧化物栅极晶体管举例图解了复合图和分层图形。

每层的图形是数字化的(数字化是图形转换为数据库)并由计算机处理的X-Y坐标的设计图。

第四章 芯片制造概述--3

光刻母版和掩膜版

光刻工艺是用于在晶圆表面上和内部产生需要的图形和尺寸。将数字化图形转到晶圆上需要一些加工步骤。在光刻制程中,准备光刻母版(reticle)是其中一个步骤。光刻母版是在玻璃或石英板的镀薄膜铬层上生成分层设计电路图的复制图。光刻母版可直接用于进行光刻,也可能被用来制造掩膜版。掩膜版也是玻璃底板表层镀铬。在加工完成后,在掩膜版表面会覆盖许多电路图形的复制(图4.15b)。掩膜版被用整个晶圆表面形成图形。(光刻母版和掩膜版的制做在十一章有详细讲述。)

图4.15解释了从电路设计到图形成行与晶圆之上的过程。光刻母版和掩膜版由工厂单独的部门制造或者从外部供应商购买。它向芯片生产部门按每种电路器件种类提供一套光刻母版或掩膜版。

晶圆制造实例

集成电路的生产从抛光硅片的下料开始。图4.16的截面图按顺序展示了构成一个简单的MOS栅极硅晶体管结构所需要的基础工艺。每一步工艺生产的说明如下:

第一步:增层工艺。对晶圆表面的氧化会形成一层保护薄膜,它可作为掺杂的屏障。这层二氧化硅膜被称为场氧化层。

第二步:光刻工艺。光刻制程在场氧化层上开凹孔以定义晶体管的源极、栅极和漏极的特定位置。

第三步:增层工艺。接下来,晶圆将经过二氧化硅氧化反应加工。晶圆暴露的硅表面会生长一层氧化薄膜。它可作为栅极氧化层。

第四步:增层工艺。在第四步,晶圆上沉积一层多晶硅作为栅极构造的。

第五步:光刻工艺。在氧化层/多晶硅层按电路图形刻蚀的两个开口,它们定义了晶体管的源极和漏极区域。

第六步:掺杂工艺。掺杂加工用于在源极和漏极区域形成N阱。

第七步:增层工艺。在源极和漏极区域生长一层氧化膜。

第八步:光刻工艺。分别在源极、栅极和漏极区域刻蚀形成的孔,称为接触孔。

第九步:增层工艺。在整个晶圆的表面沉积一层导电金属,该金属通常是铝的合金。

第十步:刻工艺。晶圆表面金属镀层在芯片和街区上的部分按照电路图形被除去。金属膜剩下的部分将芯片的每个元件准确无误地按照设计要求互相连接起来。

第十一步:热处理工艺。紧随金属刻加工后,晶圆将在氮气环境下经历加热工艺。此步加工的目的是使金属与源、漏、栅极进一步熔粘以获得更好的电性接触连结。

第十二步:增层工艺。芯器件上的最后一层是保护层,通常被称为防刮层或钝化层(在图4.5中没有列出)。它的用途是使芯片表面的元件在电测,封装及使用时得到保护。

第十三步:光刻工艺。在整个工艺加工序列的最后一步是将钝化层的位于芯片周边金属引线垫上的部分刻蚀去。这一步被称为引线垫掩膜(在图4.6中没有列出)。

这个十二步的工艺流程举例阐述了这四种最基本的工艺方法是如何应用到制造一个具体的晶体管结构的。电路所需的其它元件(二极管、电阻器和电容)也同时在电路的不同区域上构成。比如说,在这个工艺流程下,电阻的图形和晶体管源/漏极图形同时被添加在晶圆上。随后的扩散工艺形成源极/栅极和电阻。对于其它形式的晶体管,如双极型和硅晶栅极金属氧化物半导体,也同样是由这四种最基本的工艺方法加工而成,不同的只是所用材料和工艺流程。

芯片术语

图4.17是一个中等规模的金属氧化物半导体集成电路的显微照片。之所以选择这个集成等级,是为了照片上能显示出电路的具体图形。对于很高集成度的电路,它的元件非常小,以至于在整个芯片的显微照片上无法辨认。芯片的主要结构部件是:

1. 双极型晶体管

2. 电路的特定编号

3. 压焊点

4. 压焊点上的一小块污染物

5. 金属导线

6. 街区(芯片间的分割线)

7. 独立无连接的元件

8. 掩膜版对准标记

9. 电阻

晶圆测试

在晶圆制造完成之后,是一步非常重要的测试。这步测试是晶圆生产过程的成绩单。在测试过程中,每一个芯片的电性能力和电路机能都被检测到。晶圆测试也就是芯片测试(die sort)或晶圆电测(wafer sort)。

在测试时,晶圆被固定在真空吸力的卡盘上,并与很薄的探针电测器对准,同时探针与芯片的每一个焊接垫相接触(图4.18)。电测器在电源的驱动下测试电路并记录下结果。测试的数量、顺序和类型由计算机程序控制。测试机是自动化的,所以在探针电测器与第一片晶圆对准后(人工对准或使用自动视觉系统)的测试工作无须操作员的辅助。

测试是为了以下三个目标。第一,在晶圆送到封装工厂之前,鉴别出合格的芯片。第二,器件/电路的电性参数进行特性评估。工程师们需要监测参数的分布状态来保持工艺的质量水平。第三,芯片的合格品与不良品的核算会给晶圆生产人员提供全面业绩的反馈。合格芯片与不良品在晶圆上的位置在计算机上以晶圆图的形式记录下来。从前的旧式技术在不良品芯片上涂下一墨点。

晶圆测试是主要的芯片良品率统计方法之一。随着芯片的面积增大和密度提高使得晶圆测试的费用越来越大。2这样一来,芯片需要更长的测试时间以及更加精密复杂的电源、机械装置和计算机系统来执行测试工作和监控测试结果。视觉检查系统也是随着芯片尺寸扩大而更加精密和昂贵。芯片的设计人员被要求将测试模式引入存储阵列。测试的设计人员在探索如何将测试流程更加简化而有效,例如在芯片参数评估合格后使用简化的测试程序,另外也可以隔行测试晶圆上的芯片,或者同时进行多个芯片的测试。晶圆的测试良品率在第六章具体讲述。

集成电路的封装

如图4.19中演示的,绝大部分晶圆会被送到第四个制造阶段-封装(packaging)。封装厂可能与晶圆厂在一起,或者在远离的地点,许多半导体制造商将晶圆送到海外的工厂封装芯片。(封装工艺在第十八章有详细讲述)在封装过程中,晶圆被分成许多小芯片,合格的芯片被封装在一个保护壳内。也有一些种类的芯片无须封装被直接合成到电子系统中。

总结

半导体制造过程周期长而且复杂,并随着产品类型、集成等级、特征尺寸等的不同产生许多生产工艺差异。本章将半导体的制造分成四个阶段讲述会更容易理解。读者会通过认识最基本的四个工艺方法得到对对晶圆生产的进一步理解。本章利用几个简单的工艺来讲解晶圆生产的基本技术工艺。实际的各种工艺将在工艺原理章节里和第十六、十七章里重点阐述。半导体工业的驱动力和发展方向在第十五章中有论述。

关键术语和概念

芯片 光刻加工

芯片术语 工程试验芯片

电路设计的步骤 热处理加工

电路设计图厂 增层加工

电性测试厂 复合图

扩散加工

复习问题

1. 说出一种增层的工艺。

2. 离子注入属于那一种基本的工艺方法?

3. 列出最基本的四种工艺方法。

4. 将氧化/光刻/扩散的加工流程画成截面图解释。

5. 描述一下电路设计的复合图。

6. 那一种基本工艺方法用到掩膜版?

7. 在电性测试是检测以下哪一参数?(晶圆厚度,缺陷密度,电路功能)

8. 在电路设计过程的哪一步运用CAD系统?

9. 为什么要将芯片封装?

10. 晶圆制造实例所讲的接触孔是什么作用?

参考文献

4.1 R.Kopp, Kopp Semiconductor Engineering, September 1996

4.2 R. Iscoff, “VLSI Testing: The Stakes Get Higher”, Semiconductor International, September 1993, P.58

第五章 污染控制--1

概述

在这一章中, 我们将解释污染对器件工艺生产,器件性能和器件的可靠性的影响, 以及芯片生产区域存在的污染类型和主要的污染源。同时,也将对洁净室规划,主要的污染控制方法和晶片表面的清洗工艺进行讨论。

目的

完成本章后您将能够:

1. 识别污染在半导体器件及其工艺生产中的三大主要影响。

2. 列出芯片工艺生产中的主要污染源。

3. 定义洁净室的洁净等级。

4. 列举等级分别为100,10 和1的芯片生产区域的微尘密度。

5. 描述正压环境,风淋室以及粘着地板垫(译者注:FAB入口处用以粘除脚底的灰尘)在保持环境洁净度中所起的作用。

6. 列出至少三种在芯片厂中尽量减少人员污染的技术方法。

7. 识别在通常所说的水中存在的三种污染物以及在半导体生产厂中对它们的控制。

8. 描述通常所说的工业化学品和半导体级纯度的化学品之间的区别。

9. 说出两个由高静电等级引起的问题以及两种控制静电的方法。

10. 描述典型的前线和后线的晶片清洗工艺。

11. 列举典型的晶片冲洗技术。

介绍

污染是可能将新兴的芯片生产工业扼杀于摇篮中的首要问题之一。半导体工业起步于由航空工业发展而来的洁净室技术。然而,事实证明,对于大规模集成电路的生产,这些技术水平是远远不够的。除此之外,能够提供洁净室专用化学品和材料的供应商以及具备建造洁净室知识的承包商更是无处可寻。在那些年里,该工业是以家庭型规模的方式发展的。

如今,大规模的复杂的洁净室辅助工业已经形成,洁净室技术也与芯片的设计及线宽技术同步发展。通过不断地解决在各个芯片技术时代所存在的污染问题,这一工业自身也得到了发展。以前的一些小问题,有可能成为当今芯片生产中足以致命的缺陷。

问题

半导体器件极易受到多种污染物的损害。这些污染物可归纳为以下四类。分别是:

1. 微粒

2. 金属离子

3. 化学物质

4. 细菌

微粒。半导体器件,尤其是高密度的集成电路,易受到各种污染的损害。器件对于污染的敏感度取决于较小的特征图形的尺寸和晶片表面沉积层的薄度。目前的量度尺寸已经降到亚微米级。一微米(µm)是非常小的。一厘米等于10,000微米。人的头发的直径为100微米(图5.1)。这种非常小的器件尺寸导致器件极易受到由人员,设备和工艺操作用使用的化学品所产生的存在于空气中的颗粒污染的损害。由于特征图形尺寸越来越小,膜层越来越薄,所允许存在的微粒尺寸也必须被控制在更小的尺度上。

图 5.1 一微米的相对大小

图 5.2 污染物的相对尺寸

图 5.3 空气中的微粒与晶片尺度的相对大小

由经验所得出的法则是微粒的大小要小于器件上最小的特征图形尺寸的1/10倍1。直径为0.03微米的微粒将会损害0.3微米线宽大小的特征图形。落于器件的关键部位并毁坏了器件功能的微粒被称为致命缺陷。致命缺陷还包括晶体缺陷和其它由于工艺过程引入带来的问题。在任何晶片上,都存在大量的微粒。有些属于致命性的,而其它一些位于器件不太敏感的区域则不会造成器件缺陷。1994年, SIA将0.18微米设计的光刻操作中的缺陷密度定为0.06微米135个,每平方厘米每层。

金属离子。在第二章中,介绍了半导体器件在整个晶片上N型和P型的掺杂区域以及在精确的N/P 相邻区域,都需要具有可控的电阻率。通过在晶体和晶片上有目的地掺杂特定的掺杂离子来实现对这三个性质的控制。非常少量的掺杂物即可实现我们希望的效果。但遗憾的是,在晶片中出现的极少量的具有电性的污染物也会改变器件的典型特征,改变它的工作表现和可靠性参数。

可以引起上述问题的污染物称为可移动离子污染物 (MICs)。它们是在材料中以离子形态存在的金属离子。而且,这些金属离子在半导体材料中具有很强的可移动性。也就是说,即便在器件通过了电性能测试并且运送出去,金属离子仍可在器件中移动从而造成器件失效。遗憾的是,能够在硅器件中引起这些问题的金属存在于绝大部分的化学物质中。所以,在晶片中,MIC污染物必须被控制在1010原子/cm²的范围内甚至更少。2

每10亿个单位中的金属含量 (ppb) 杂质钠 50钾 50铁 50铜 60镍 60铝 60镁 60铅 60锌 60 氯 1000

图 5.4 光刻胶去除剂的金属含量(EKC Technology – 830 光刻胶去除剂)

钠是在未经处理的化学品中最常见的可移动离子污染物,同时也是硅中移动性最强的物质。因此,对钠的控制成为硅片生产的首要目标。MIC的问题在MOS器件中表现最为严重,这一事实促使一些化学品生产商研制开发MOS级或低钠级的化学品。这些标识都意味着较低的可移动污染物的等级。

化学品。 在半导体工艺领域第三大主要的污染物是不需要的化学物质。工艺过程中所用的化学品和水可能会受到对芯片工艺产生影响的痕量物质的污染。它们将导致晶片表面受到不需要的刻蚀,在器件上生成无法除去的化合物,或者引起不均匀的工艺过程。氯就是这样一种污染物,它在工艺过程中用到的化学品中的含量受到严格的控制。

细菌。 细菌是第四类的主要污染物。细菌是在水的系统中或不定期清洗的表面生成的有机物。细菌一旦在器件上形成,会成为颗粒状污染物或给器件表面引入不希望见到的金属离子。

污染引起的问题

这四种污染物在以下三个特定的功能领域对工艺过程和器件产生影响。它们是:

1. 器件工艺良品率

2. 器件性能

3. 器件可靠性

器件工艺良品率

在一个污染环境中制成的器件会引起多种问题。污染会改变器件的尺寸,改变表面的洁净度,并且/或者造成有凹痕的表面。在晶片生产的过程中,有一系列的质量检验和检测,他们是为检测出被污染的晶片而特殊设计的。高度的污染使得仅有少量的晶片能够完成全工艺过程,从而导致成本升高。

器件效能

一个更为严重的问题是在工艺过程中漏检的小的污染。晶片看起来是干净的,但其中的未能检测出来的颗粒,不需要的化学物质,和/或高浓度的可移动离子污染物,可能会改变器件的电性能。这个问题通常是在芯片切割时的电测试中显现出来。

器件可靠性

最令人担心的莫过于污染对器件可靠性的失效影响。小剂量的污染物可能会在工艺过程中进入晶片,而未被通常的器件测试检验出来。然而,这些污染物会在器件内部移动,最终停留在电性敏感区域,从而引起器件失效。这一失效模式成为航空业和国防业的首要关注。

在这一章的余下部分,将讨论对半导体器件生产中产生影响的各类污染的来源、性质及其控制。随着二十世纪七十年代LSI电路的出现,污染控制成为这一工业的根本。从那时起,大量的关于污染控制的认识逐渐发展起来。如今污染的控制本身成为一门学科,是制造固态器件必须掌握的关键技术之一。

在这一章中讨论的污染控制问题适用于芯片生产区域、掩膜生产区域、芯片封装区域和其他一些生产半导体设备和材料的区域。

污染源

普通污染源

洁净室内污染源是指任何影响产品生产或产品功能的一切事物。由于固态器件的要求较高,所以就决定了它的洁净度要求远远高于大多数其它的工业的洁净程度。实际上生产期间任何与产品相接触的物质都是潜在的污染源。主要的污染源有:

1. 空气

2. 厂务设备

3. 洁净室工作人员

4. 工艺使用水

5. 工艺化学溶液

6. 工艺化学气体

7. 静电

每种污染源产生特殊类型和级别的污染,需要对其进行特殊控制以满足洁净室的要求。

空气

普通空气中含有许多污染物,只有经过处理后才能进入洁净室。最主要的问题是含有在空气中传播的颗粒,一般指微粒或浮尘。普通空气包含大量的微小颗粒或粉尘,见图5.5。 微小颗粒(悬浮颗粒)的主要问题是在空气中长时间飘浮。而洁净室的洁净度就是由空气中的微粒大小和微粒含量来决定的。

美国联邦标准209E 规定空气质量由区域中空气级别数来表示。3 标准按两种方法设定,一是颗粒大小,二是颗粒密度。 区域中空气级别数是指在一立方英尺中所含直径为 0.5 微米或更大的颗粒总数。一般城市的空气中通常包含烟,、雾、气。每立方英尺有多达五百万个颗粒, 所以是五百万级。随着芯片部件尺寸的更新换代,不断提高的芯片灵敏度要求越来越小的颗粒。4

图示5.6表显示了标准 209E 规定的颗粒直径与颗粒密度的关系。图示5.7 列出了不同环境下洁净度级别数与对应的颗粒大小。联邦标准209E规定最小洁净度可到一级。因为 209E 以 0.5 微米的颗粒定义洁净度,而成功的晶圆加工工艺要求更严格的控制,所以工程技术人员工程师们致力于减少10级和1级环境中0.3 微米颗粒的数量。例如: Semetech/Jessi 建议 64 兆内存加工车间为 0.1 级,256 兆为 0.01 级。5

图5.5 空气中颗粒的相对尺寸 (微米)

Aerosols浮质 Metallurgical Dust金属尘埃

Cement Dust水泥尘埃

Tobacco Smoke烟尘 Insecticide Dust杀虫剂微粒

Human Hair Diameter人类毛发的直径

图5.6 空气洁净等级标准 209E

Proposed Federal Standard 209E

建议联邦标准 209E

Airborne Particulate Cleanliness Classes for Clean Rooms and Clean Zones

洁净室与洁净区的空气颗粒洁净等级

Class1, 10, 100, 1000, 10000, 100000

一级,十级,百级,千级,万级,十万级

Particles size (micrometer)

颗粒尺寸 (微米)

Class limits in particles per cubic foot of size equal to or greater than particles sizes shown

洁净等级是指一平方英尺中颗粒尺寸等于或大于图中所示颗粒尺寸

*The class limit particle concentrations shown are defined for class purposes only and do not necessarily represent the size distribution to be found in any particular situation

图中所示洁净等级所指颗粒含量只用于等级定义,并不代表任何特定环境下的尺寸分布

图 5.7 不同环境的典型级别数

Enviroment环境

Class Number 级别数

Maximum particle size (micron) 最大颗粒尺寸限度(微米)

Projected-256 Mbit 256兆内存加工车间

Mini enviroment微环境

ULSI Fab超大规模集成电路加工车间

VLSI Fab特大规模集成电路加工车间

VLF station Assembly area空气层流立式工作台装配区

House room库房

Outdoors室外

第五章 污染控制--2

by r53858

净化空气的方法

洁净室的设计是要使生产免污染晶圆的能力更完整化。设计时的主要思路是保持加工车间中空气的洁净。自动化生产也是降低污染的一种重要方法。这个问题将于“工艺设备”一节与第十五章展开讲述。共有四种不同的洁净室设计方法:

1. 洁净工作台

2. 隧道型设计

3. 完全洁净室

4. 微局部环境

洁净工作台法

空气经过过滤的生产环境首先被航空航天工业使用。即使一个极其微小的缺陷都可造成卫星工作失误,因此,NASA (译者注:美国航空航天中心)和其服务商们建造了带有过滤天花板夹层和过滤墙体的车间。而且首创了许多基本的污染控制理念,其中包括从工作人员洁净服到洁净室使用物的管理方法。

半导体工业采用了许多这方面的技术。 然而一个主要的问题是当从小加工车间扩建为有更多工人工作的大型车间后,很难保持其固有的洁净度。 早期半导体工业把带过滤天花板夹层和墙体的方法演化为洁净工作台法。这个主要是把过滤器装在单个工作台上,并使用无脱落的物质。 在工作台以外,晶圆被装在密封的盒子中储存、运输。

在大型车间中按顺序排列的工作台(叫做工作罩)组成加工区,使晶圆依工艺次序经过而不从露于空气中。洁净工作罩中的过滤器是一种高效颗粒搜集过滤器(HEPA过滤器)。这些过滤器是由含许多小孔,并按手风琴琴叶折叠的脆性纤维组成(见图示5.8),由于高密度的小孔与大面积的过滤层,使得大量的空气低速流过。由于低速空气可避免产生空气流,有利于工作台的洁净度,并且对于操作员而言,在舒适的环境中工作也是必要的。典型的空气流量6为每分钟90到100 英寸。HEPA过滤器可达到99.99%或更高的过滤效率,并可用于三种净化方法中。

一般来说,HEPA过滤器装于洁净工作台顶部见图5.9。空气由风扇吸入先通过前置过滤器,再通过HEPA过滤器,并以均匀平行的方式流出,在工作台表面改变方向,流出工作台。安装档板可控制晶圆表面空气流动方向,通常这种方式称为空气层流立式式(VLF)工作台,它是由空气流的方向命名的。有些工作台把HEPA过滤器装于工作台后部,这种方式被称为空气层流平行(HLF)式工作台。

图5.8 高效颗粒搜集过滤器(HEPA)

Dirty Air脏空气

Clean Air净空气

图5.9空气层流立式工作台截面图

Blower鼓风机

HEPA Filter HEPA过滤器

Prefilter前级过滤器

Shield挡板

Air Flow空气流

Work Surface工作台面

这两种工作台按两种方法来保持晶圆清洁:首先是工作台内的空气净化;其次,净化过程在工作台内产生一点空气正压,正压可防止由操作员与走廊产生的污染物进入工作台。

使用化学溶液的工艺需要对VLF式工作台进行特殊设计(见图5.10), 这种工作台必须接有空气排风,以吸收化学溶液蒸汽,因为蒸汽会产生安全及污染的危险。在这种设计下,必须平衡VLF与排风中的空气流,来维持工作台的洁净级别数。而且还要求晶片需存放在工作台中相对较洁净的前部。

净化工作台的方法还可应用于现代晶圆加工设备中。在每台设备上安装VLF或HLF式工作台来保持晶圆在装卸过程中洁净。

隧道/车间概念

随着更严格的颗粒控制成为必要,VLF型工作台就产生了一些缺点。其中主要是由于车间中众多工作人员的移动而产生的易污染性。进出于加工车间的工作员对所有流程的工作台都存潜在污染。

把加工车间分割为不同的隧道可解决人员污染问题(图5.11)。这时过滤器被装于车间天花板上,而不是在单独工作台中,但是起的作用相同。经过天花板中的过滤器流入的空气可保持持续洁净,并且会降低人员产生的污染,这是因为减少了工作台周围的工作人员。但这种方法的缺点是建造费用较高,而且不适于工艺改动。

图 5.10立式空气层流-蒸气-排风工作台截面图

To Factory Exhaust System到工厂排风系统

Air Flow空气流

Fumes蒸气

Chemical Beaker化学品容器

图 5.11隧道型洁净室截面图

HEPA Filters HEPA过滤器

Clean Air 洁净空气

Process Work Station

工艺工作台

完全洁净室方法

洁净室设计和过滤技术的发展,允许我们又回到敞开式加工区域的建设(见图5.12), 在最先进的设计中,空气过滤包括天花板中的HEPA过滤器,并从地板上回收空气,保持持续的洁净空气流。工作台顶部带有贯通穿孔,可使空气无阻碍地流过。

图5.12 洁净室空气层流截面图(国际半导体版权所有)

Fresh Air新鲜空气

Fan风扇

Service Chase维修区

Slab Floor混凝土层

Plenum高压区

HEPA Filters HEPA过滤器

Clean Room洁净室

Equip设备

Optical Equip光学设备

Perforated Floor过孔层

Vibration-stiff optical mount防阵支架

Fan 风扇

Service Chase维修区

一个重要的洁净室参数是再循环利用度。这个参数是指在人员换班、人员休息或其他干扰因素之外,空气通过过滤器回到洁净室以满足要求所需的时间。在一级洁净车间中,空气每六秒钟循环一次。7

设备与厂务系统的设计趋势是要隔离晶圆与污染源。VLF式洁净罩隔离了晶圆与室内空气,隧道设计隔离了晶圆与大量的人员流动。CMOS(互补型场效应晶体管)集成电路的出现增加了工艺流程,而且也增加了洁净室中的设备。这样就使加工车间的面积加大而增加了潜在的污染源,包括大量的空气和增加的工作人员。但这些变化使得洁净室的建造费用高达几十亿美金。

微局部环境

二十世纪八十年代中期的研究显示洁净室建造费用的增加,降低了公司的回报率。所以新的方向是把晶圆密封在尽量小的空间成为新的发展方向。这项技术已应用于曝光机和其他的工艺之中,它们为晶圆的装卸安装了洁净的微局部环境(图5.13)。

但挑战是为使晶圆不暴露于空气中,需要把一系列的微局部环境连在一起。惠普公司在二十世纪八十年代中期发明了一种重要的连接装置“标准机械接口装置”(SMIF)8。 利用SMIF,封闭的晶圆加工系统代替了传统的运输盒,并用干净空气或氮气来在系统中加压以保持清洁。这种方法就是“晶圆隔离技术(WIT)”或“ 微局部环境”的一种。这个系统包含三个主要部分:传输晶圆的晶圆盒或叫POD,设备中的封闭局部环境,和装卸晶圆的机械部件。 POD就作为与工艺设备的微局部环境相连的机械接口。 在工艺设备的晶圆系统上,特制的机械手把晶圆从POD中取出或装入。另一种方法就是利用机械手把晶片匣和从POD中取出送入工艺设备的晶圆处理系统中。为局部环境可提供更优的温度与适度控制。

图 5.13 Wafer transfer microenvironment芯片传输微环境

Isolation pod with vaccum or inert atmosphere带真空或惰性气体的隔离POD

Standard mechanical interface (SMIF) 标准机械接口装置(SMIF)

晶圆隔离/微局部环境技术还有利用其他方法升级现存制造工厂的优点(图5.14)。因污染而损失的成品率可降低,这个优点即使在小型工厂或费用较低时也可使用。WIT可使空气洁净度达到较高的要求,并可降低建造和生产费用。因为晶圆已被隔离,所以就减轻了对工作服、工作过程和各种其它限制的要求。然而随着大尺寸晶圆的出现,增加了POD的重量,这对操作人员来讲也过重,增加了滑落后的损失,这反而增加了机械手的建造费用与复杂性。微局部设计规划还要考虑等待加工的晶圆存储问题。现行的技术使用储存柜来存储等待的加工晶圆与POD,布局的规划可能还包括一个存储中心,每台设备上有或没有缓冲存储区。

图 5.14 Minienvironment system elements微环境系统部件

Process chamber工艺反应室

Environmentally controlled chamber with wafer load/unload system带上下料系统的环境控制反应室

Isolation pod w/vacuum or inert atmosphere 带真空或惰性气体的隔离POD

Wafer cassette晶片匣

Standard mechanical interface (SMIF) 标准机械接口装置(SMIF)

温度, 湿度及烟雾

除了控制颗粒,空气中温度,湿度和烟雾的含量也需要规定与控制。温度控制对操作员的舒适性与工艺控制是很重要的。许多利用化学溶剂来做刻蚀与清洗的工艺都在没有温度控制的设备箱内完成,只依赖于洁净室温度的控制。这种控制非常重要,因为化学反应会随温度的变化而不同,例如,每升高十摄氏度,刻蚀速率参数加二。通常的室温为72华氏度,上下幅度两度。

相对湿度也是一个非常重要的工艺参数,尤其在光刻工艺中。 在这个工艺中,要在晶片表面镀上一层聚合物作为刻蚀膜版。如果湿度过大,晶圆表面太潮湿,会影响聚合物的结合,就象在潮湿的画板上绘画一样。如果湿度过低,晶圆表面就会产生静电,这些静电会从空气中吸附微粒。一般相对湿度应保持在15%到50%之间。

烟雾是洁净室的另一个空中污染源。而它同样对光刻工艺影响最大。光刻中的一个步骤与照相中的曝光相似,是一种化学反应工艺。臭氧是烟雾中的主要成分,易影响曝光,必须被控制。在进入空气的管道中装上碳素过滤器可吸附臭氧。

第五章 污染控制--3

r53858

洁净室的布局

传统的洁净室布局是舞厅式的设计。它由各个工艺隧道向中央走廊敞开的方式组成。现代设计是由一些小型局部洁净车间或主要工艺区域围绕着一个中心地区组成,而由中心地区提供物料和人员。 这种规划一般设计为两层,厂房第一层安置厂务设备与物料,第二层是加工车间。 现在有一种三层加工车间的概念,厂务设备分装在第一、二层,这种方法的优点就是降低整体厂房占地面积。

洁净室的建设

净化空气方法的选择是洁净室设计的首要问题。每个洁净室都要在洁净程度与建造费用中找到平衡。不论最终的设计如何,每个洁净室的建造都有其基本原则。主要是需要有一个封闭的房间,由非污染物建造并能提供洁净的空气,还包括可以防止由外界或操作人员带入的意外污染。

建筑材料

洁净室的所有建造材料都由不易脱落的材料建造。这包括墙壁、工艺加工设备材料和地板。所有的管道孔都要密封,甚至灯丝都要有固态封罩。另外, 设计还要减少平滑的表面以减少灰尘的沉积,由此,不锈钢材料就广泛地被用于制造工作台。

洁净室要素

洁净室的设计和操作过程都必须防止外界污染的入侵。图5.15 显示了一个典型的加工工艺区域的规划图。有九种控制外界污染的技术,它们是:

1. 粘着地板垫

2. 更衣区

3. 空气压力

4. 空气淋浴器

5. 维修区

6. 双层门进出通道

7. 静电控制

8. 净鞋器

9. 手套清洗器

粘着地板垫。 在每个洁净室入口处放置一块带有粘性地板垫,它可把鞋底的脏物粘住,并保留下来。在有些洁净室里,整片地板的表面都被处理过以收集脏物。大多地板垫都分许多层,当上一层变脏后,可撕掉而露出下一层。

图 5.15 FAB区域及更衣区, 空气淋浴, 维修区

Factory工厂

Lockers存储柜

Bench板凳

Gowning Area更衣区

Air Shower空气淋浴

Service Aisle维修区

Access to Maintain Equipment 维修设备入口

Fab Area FAB区域

Pass-through for Chemicals化学品进出通道

Service Aisle维修区

更衣区。 洁净室的重要部分是更衣区或前庭。这个区域是洁净室与厂区的缓冲部分,这个区域通常通过天花板中的HEPA过滤器提供空气。在这个区域,工作人员的洁净服存储在贮衣箱内。并且工作人员在此区域换上洁净服。这个区域的洁净度控制应依据不同的洁净室的洁净度而不同。但大多数工厂采用与洁净室相同的要求。此区域利用长凳分为两部分,工作人员在一侧穿上洁净服,而在长凳上穿戴鞋套,这样做目的是保持长凳与洁净室的区域更干净。

一个好的洁净室的管理程序要求厂区和洁净室的之间门永远不能同时打开,目的是洁净室不能暴露于厂区的污染环境中。洁净室的管理还包括洁净室物品与衣物的管理,包括进入物与禁入物清单,而有些区域还在走廊提供更衣柜,等等。

空气压力。 平衡洁净室、更衣间和厂区之间的压力也是设计中主要的部分。优秀的厂房设计要求三个区域的空气压力要平衡,已达到洁净室的空气压力最高,更衣间次之,而厂区和走廊最低。当洁净室的门打开时,相对的高压可防止空气灰尘进入。

风淋室。 洁净室设计的最后部分是在洁净室与更衣间之间建造一个风淋室。洁净室工作人员进入淋浴间,高速流动的空气吹掉洁净服外面的颗粒。并且风淋间装有互锁系统,防止前后门同时打开。

维修区。 洁净室实际上是一系列房间,这一系列的每一间都是作为洁净室的维修区域。中央是工艺洁净室,周围是维修区,按照指定的洁净级别维护,一般来讲要求它的洁净级别数高于洁净室(译者:洁净度低)。通常维修区域的级别为1000或 10000级,这里包括工艺化学品传输管道、电缆和洁净室物品。主要工艺设备装于墙后的维修区内,面对洁净室,这样可使技术员在洁净室外维护设备,而不必进入洁净室。

双层进出通道。维修区还可做为次洁净室来贮存物料和供给,它们通过双层进出通道进入洁净室,这可保持洁净室的洁净度。进出通道可以是一个双层门的盒子,或者是供给正压过滤空气, 并有防止进出门同时打开的互锁装置。通常进出通道装有HEPA过滤器,所有进入洁净室的物品与设备都须在进入前经过净化。

静电控制。次微米级晶圆集成电路越密,就越容易收到静电吸附到晶圆表面的较小微粒的影响。 静电可产生于晶圆、存储盒、工作台表面与设备上。这些物体表面可产生高达50000伏的静电电压,它可从空气和工作服中吸附尘埃。这些尘埃可污染到晶圆,而且静电吸附的颗粒很难用标准的刷或湿洗的方法去除。

图 5.16摩擦电荷序列(混合电路技术手册, Noyes出版)

Increasingly Positive正电荷增加

Increasingly Negative负电荷增加

Air空气

Human Skin皮肤

Glass玻璃

Human Hair头发

Nylon 尼龙

Wool毛制品

Lead石墨

Aluminum铝

Paper纸

Steel钢

Cotton棉制品

Steel钢

Hard Rubber硬橡胶

Nickel-copper镍铜合金

Brass-silver铜银合金

Synthetic Rubber合成橡胶

Polyurethane聚亚安酯

Polypropylene 聚丙稀PVC聚稀氯乙稀

Silicon硅

Teflon聚四氟乙烯

大多数静电都是由摩擦产生。当两个原本为一体的物体分开时就会产生静电。物质一面因损失电子而带正电,另一面因得到电子而带负电。图5.16表示了在洁净室中的物质经过摩擦后而产生的正负静电表9。

静电还会对电子元器件的性能有影响。特别是对MOS栅级的电介质层的影响。静电放电电流(ESD)会产生高达10安培的电流。这种级别的ESD可损坏MOS管与电路。ESD对元件的封装区域也有特别的影响,这样就要求在敏感的元器件,如大矩阵内存的加工和运输中采用防静电装置。

光刻掩膜工艺的掩膜版对ESD也非常敏感。放电可汽化并损坏镀铬掩膜层。

有些设备故障也与静电有关,特别是机械手、晶圆传送器、测量仪器。晶圆通常是由PFA材料制的机械手送入设备中。这种材料是防化学腐蚀的,但不导电。静电存在晶圆里,但无法从机械手散失。当机械手靠近设备的金属部分时,晶圆表面的静电就会对设备放电,产生的电磁干扰就会影响设备的正常工作。

静电控制包括防止静电堆积和防止放电两种技术(图5.17)。防静电堆积技术包括使用防静电物质制造的工作服和使用加工时的存储盒。 一些区域中,在墙壁中使用防静电物质来防止静电的堆积,在墙壁表面涂上中和物质来达到此目的。通常, 这项技术不用于重要的工艺车间,因为中和物质一般会产生污染。

图 5.17静电消除技术

Ionizing Grid电离栅板

Air Flow空气流

VLF Station空气层流立式工作台

Grounded Wrist Strap接地腕带

In Line Ionizing Unit在线电离件

Grounded Mat接地站垫

放电技术包括使用电离器和使用静电接地带。电离器一般置于HEPA过滤器的下面, 中和在过滤器上堆积的静电。有时还置于氮气吹扫枪中起相同的作用。有些工作台还装有手提式电离器,向加工中晶圆吹送离子空气。静电放电还通过为操作员带上接地腕带,在重要的工艺工作台使用接地垫,使工作台本身接地。最先进的加工厂有一套复杂的静电控制程序,包括防止静电累积、防止静电放电、操作人员培训和第三方监督等。

净鞋器。在所有的污染控制区,最脏的是地板。在进入洁净室的门口,净鞋器利用旋转的毛刷来去除鞋侧与鞋套的灰尘。一般的净鞋器带有内置的真空系统来收集刷落的颗粒,还有收集袋来收集灰尘。10

手套清洗器。在加工区保持使用洁净的手套也是一个问题。有一种方法是当手套被污染时,应要求操作员立即废弃手套。但是有些污染无法用肉眼看到,所以操作员废弃手套的决定就因人而异。另外也可规定在每次换班时必须换手套,但这使得费用升高。有些加工厂使用手套清洗器,在密闭的空间内清洗并烘干手套。11

人员产生的污染

洁净室工作人员是最大的污染源之一。即使一个经过风淋的洁净室操作员,当他坐着时,每分钟也可释放十万到一百万个颗粒。12当人员移动时,这个数字还会大幅增加。当一个人以每小时两英里的速度走动时,他每分钟会释放高达五百万个颗粒,这些颗粒都是来自坏死的头发和脱落的皮肤。其它的颗粒源还有喷发胶、化妆品、染发和暴露的衣服。图5.18列出了从不同的操作人员的动作中产生的污染物的水平。13

普通的衣服,即使在洁净服内,也会给洁净室增加上百万个微粒。在洁净度非常高的洁净室内,操作员只能穿用无脱落材料而且编织紧密的衣服。而用毛线和棉线编织的服装则被禁止,而且洁净服要制成高领长袖口的。

人类的呼吸也包含着大量的污染,每次呼气向空气中排出大量的水汽和微粒。而一个吸烟者的呼吸在吸烟后在很长时间里仍能带有上百万的微粒。而体液,例如含钠的唾液也是半导体器件的主要杀手。健康的人是许多污染的污染源,而病人就更加严重了。特别是皮疹与呼吸传染病患者还会产生额外的污染源。一些制造厂对患特定病症的工作人员进行另行安排。

从总体来看,唯一使工作人员适于洁净室工作的可行的办法是把人员完全包裹起来。而且洁净室工作人员的洁净服材料因洁净度的要求不同而不同。对一个典型的洁净区(图5.18)服饰材料应不易产生脱落,并且含有导电的纤维以对释放静电。一般使用材料为聚酯与GORETEXTM。还要要求权衡材料的过滤能力与操作员穿戴的舒适度。与手套一样,重新清洗还是一次性废弃,在洁净服的使用中也是难以抉择,大多数ULSI加工厂发现可以再利用的洁净服,即使有一定的清洗费用,也可降低整体费用14。

身体的每一部分都要被罩住。头部要用内帽来罩住头发,外面再套一层外罩,外罩的设计与脸部相适合,并带有披肩,以确保用工作服盖住披肩以压住头罩。面部用面罩来罩住,面罩有各种式样,从手术医师式到完全的滑雪式。在一些洁净室,内部与外部面罩同时使用。眼睛也是产生液态微粒的主要来源,用带有侧翼的眼镜盖住(通常是安全眼镜)。在控制污染非常重要的区域,操作人员带有完全防护罩,可完全盖住头和脸部。以宇航服的头套为模型,衣服可接有过滤带、吹风机和真空系统。新鲜空气由真空泵提供,而过滤器保证呼出气体的污染物不被吹进洁净室。15

图 5.18 引发微粒增加的活动(混合电路技术手册, Noyes出版)

Normal Breath正常呼吸

No Particles无微粒

Smoker’s Breath after Smoking吸烟后吸烟者的呼吸

Sneezing喷嚏

Sitting Quietly 安坐

Rubbing Hands On Face手摩擦脸

Walking步行

Stamping Foot on Floor用脚跺地板

完全罩住身体的服装(巴尼服),可罩住腿、胳膊和脖子,设计较好的工作服要把拉锁也盖住,而且没有外面的口袋。

脚也用鞋套盖住,有的还带有连到小腿的护腿。在对静电敏感的区域,还有静电带用以释放放静电电压。

手要至少带上一副手套。大多使用是医用型 PVC 手套,这种手套的触觉感觉舒适。操作化学品时使用的手套的材料有桔红色的橡胶手套(防酸),绿色的氰橡胶手套(防溶剂)和银色的多层PVA手套。(防特殊溶剂)16。有些区域,内部可戴一副棉质手套以便穿戴舒适。手套应拉长压住袖口,防止使手臂上的污染物进入洁净室。

皮肤脱落物可用特制的润肤品进一步控制,这种润肤品能够使皮肤湿润,但它不能包含盐分和氯化物。

总之,穿衣的顺序应该是从头向下穿,这样处理是使在上一步所扬起的灰尘用下一部位的服饰盖住。而最后带上手套。控制来自洁净室的工作人员污染的特殊洁净服装与穿戴程序是众所周知的,不过最有效的预防手段就是对操作人员的培训和操作人员的落实情况。区域中工作人员对洁净室的纪律要求很容易松懈,而使洁净室的污染度升高。

第五章 污染控制--4

by:53858

工艺用水

在晶圆制造的整个过程中,晶圆要经过多次的化学刻蚀与清洗,每步刻蚀与清洗后都要经过清水冲刷 。在整个的制造过程中,晶圆总共要在冲洗的系统中待上好几个小时,一个现代的晶圆制造厂每天要使用多达几百万加仑的水,这样实际上产生了一个投资项目,包括水的加工处理、向各个加工工艺区的水的传输、废水的处理与排放17。由于半导体器件容易受到污染,所以所有工艺用水,必须经过处理,达到非常严格的洁净度要求。

城市系统中的水包含大量的洁净室不能接受的污染物:

1. 溶解的矿物

2. 颗粒

3. 细菌

4. 有机物

5. 溶解的氧气

6. 二氧化碳

普通水中的矿物质来自盐份,盐份在水中分解为离子。例如,食盐(氯化纳)会分解为钠离子和氯离子。每个都是半导体器件与电路的污染物。反渗透(RO)和离子交换系统可去除离子。

去除带电离子工艺,使水从导电介质变成阻抗,这样可用于提高去离子(DI)水的质量,去离子水在25摄氏度时的电阻是18,000,000W·Cm,也就是一般称为18兆欧姆。图5.19显示了当水中含有大量不同的溶解物质时的电阻值。

图 5.19水的电阻相对于溶解固体的含量

Resistivity Ohms-cm 25°C

电阻Ohms-cm 25°C

Dissolved Solids (ppm) 溶解固体的(ppm)

图 5.20动态随机存取存储器(DRAM)的工艺水规格(Semiconductor International, 1994年7月,第178页)

Contaminant杂质

Resistivity (MWcm) 电阻(兆欧姆)

TOC(micro-g/L) TOC(微克/升)

Bacteria (#/liter)细菌(数量/升)

Particles微粒(数量/毫升)

Critical Size (micron)

重要(微粒)尺寸(微米)

Dissolved oxygen (micro-g/l) 溶解氧(微克/升)

Sodium (micro-g/l)钠(微克/升)

Chlorine (micro-g/l)氯(微克/升)

Manganese (micro-g/l)锰(微克/升)

在制造区域的许多地方都监测工艺用水的电阻,在VLSI制造中,工艺水的目标与规格是18兆欧姆,但其他一些制造厂也使用15兆欧姆的工艺水。固态杂质(颗粒)通过沙石过滤器、泥土过滤器与次微米级薄膜从水中去除。水是细菌和真菌的避难所。细菌和真菌可由消毒器去除,这种消毒器使用紫外线杀菌,并通过水流中的过滤器滤除。

有机污染物(植物与排泄物)可通过碳类过滤器去除。溶解的氧气与二氧化碳可用forced draft decarbonators和真空消除毒气剂去除。18图 5.20显示了4MB DRAM 制造厂的工艺水规格。

清洁工艺用水至可接受的洁净水平所需的费用是制造厂的一个主要营运费用。在大多数制造厂里,工艺加工站装配有水表来检测使用后的水。如果水质降到一定的水平,就需要在净化系统中再循环净化使用。多余的脏水需依照法规规定处理,再排出工厂。一个典型的制造厂水系统如图5.21所示。在系统中存贮的水用氮气覆盖以防止二氧化碳溶于水中,水中的二氧化碳会干扰电阻值的测量引起错误读数。

工艺化学品

在制造工厂中,用于刻蚀和清洗晶圆和设备的酸、碱、溶剂必需是最高纯度的。涉及的污染物有金属离子微粒和其它化学品。与水不同的是,工艺化学品是采购来的,直接运输到工厂后使用。工业化学品分不同级别,他们分一般溶剂、化学试剂、电子级和半导体级。前两种对于半导体使用来说过脏,电子级与半导体级相对洁净些,但不同制造商所生产化学品的洁净度也是不同的。

图 5.21 典型去离子水系统

Purity Water纯水

Particle Prefilter 颗粒前过滤器

Reverse Osmosis Demineralizer反渗透去微粒器

Primary Demineralizer主要去微粒器

N2氮气

Storage Tank存储罐

Polishing Demineralizer去微粒器

Ultraviolet Sterilizer紫外线杀菌

Final Filter最终过滤器

Process Area工艺区

Recycle Loop再循环回路

Acid Neutralization酸中和

Drain排水

象SEMI这样的商业组织为整个行业建立了洁净度的规格,但是大多数半导体厂按照自己内部的规格采购化学品。化学品的主要污染是移动的金属离子,通常须限制为百分之一( PPM)级或更低。一些供应商可制造MIC级的化学品,含量仅仅十亿分之一。微粒过滤器的级别被规定为0.2微米或更低。

化学品的纯度由成份来表示。成份数就是指容器内所含化学品的百分数。例如,一瓶99.9%的硫酸表示含有99.9%的纯硫酸和0.01%的其他溶液。

把化学品传输至工艺加工区域不只包括保持化学品的洁净,还包括对容器内表面的清洁、使用不易溶解的材质的容器、不产生微粒的标识牌,并在运输前把瓶放置化学品袋中。化学品瓶现只用于老式、技术较低的制造厂中。

许多公司采用大量购入方式买入洁净工艺化学品,然后倒入小罐中,并通过管道从中央系统传入工艺工作台,或者从小瓶直接传输到工艺工作台。大量化学品传输系统(BCDS)可以提供更洁净的化学品且费用较低。另外特别要注意定期清洁管道和运输瓶来防止污染。另一个特殊问题是当把化学品倒入另一种化学品瓶中时会产生交互污染。每种化学品的化学品瓶应专用。---

有几种技术可以同时满足更洁净的化学品、更严格的工艺控制和较低的费用。其中一种是点使用(POU)化学品混合器(BCDS的另一版本)。这种装置连接在湿洗柜或自动机械上,混合化学品后把他们送到工艺罐中。另一种就是化学品再加工系统,这种装置设于湿工艺工作台的排水系统中。去除离子的化学品被再过滤或者在某些情况下需再加入离子重新使用。重要的“再利用刻蚀器”要接上过滤器以保证为晶圆提供洁净的化学品源。一种更新的工艺是点使用化学品再生(POUCG)。例如氨水,氢氟酸和过氧化氢这些化学品是由相应的气体与去离子水在工艺工作台混合而成,这种方法可以减少化学品包装与运输时所产生的污染,可制造出万亿(ppt)级的化学品。19

化学气体

除了许多湿(液体)化学品工艺制程,半导体晶圆还要使用许多气体来加工。这些气体有从空气中分离出来的如氧气、氮气和氢气,还有特制的气体如砷烷和四氯化碳。

和化学品一样,气体也必须清洁地传输至工艺工作台与设备中。气体质量由以下四项指标来衡量:

1.纯度

2.水气含量

3.微粒

4.金属离子

所有工艺气体都要求极高的纯度,用于氧化、溅射、等离子刻蚀、化学气相沉积(CVD)、活性离子刻蚀、离子注入和扩散等工艺的气体也有特殊要求。所有涉及化学反应的工艺都需要能量。如果工艺气体被其它气体污染,则预期的反应就会产生显著改变,或者在晶圆表面的反应结果也产生改变。例如,一罐溅射工艺用氩气里如果有氯杂质,就会导致生成的溅射薄膜有影响器件的恶果。气体纯度由成份数表示,纯度一般从99.99%到百分之99.999999% ,取决于气体本身和该气体在工艺中的用途。纯度由小数点右边的九的位数表示,最高纯度级别可为“6个9纯”。20

保持气体从生产商到工艺工作台过程中不变的纯度是对晶圆制造厂的一个挑战。从生产源开始,气体要通过管道系统、带有气阀与流量表的气柜,然后接入设备。这整个系统中的任何一部分的泄漏都是灾难性的。外部气体(特别是氧气)进入工艺气体参加化学反应,就改变了反应气体的成分,也改变了期望的化学反应。气体的污染还可以由系统本身散气而产生。一个典型的系统设有不锈钢管道与阀门,还有聚脂材质的部件,如接头与密封件。对于超级洁净系统,不锈钢表面还须经过电子抛光,和(或)用真空双层保护表面内部的熔接点以减少散气。21 另一种技术就是在表面长一层离子氧化膜,以进一步减少散气。这种技术一般称为氧气钝化(OP)。要避免使用聚脂物质。气体柜的设计减少了可堆积污染的死角。另外洁净焊接工艺的使用也非常重要,杜绝了焊接气体被吸入气体管道。

水汽的控制也是非常重要的。水蒸汽是一种气体,和其它污染气体一样,也会参与不需要的反应。在晶圆制造厂中加工晶圆时带有水汽特别是个问题。当有氧气或水分存在时,硅很容易氧化。所以控制不需要的水汽对阻止硅表面的氧化是非常重要的。水汽的上限一般是3到5ppm。

在气体中有微粒或金属离子会产生与化学溶剂的污染相同的影响,气体最终会过滤至0.2微米级,而金属离子也要被控制在百万分之一以下。

由空气中分离的气体以液态形式存贮于厂区里,在这种状态下,气体温度很低,而且这种状态可冷冻许多杂质并贮存于罐底部。特殊气体是以高压瓶的形式采购来的。因为特殊气体大多是有毒或易燃的,所以一般贮存在厂区外的特制的气柜中。

石英。 晶圆有大量的工艺时间是在石英器中度过的,例如,晶圆固定器、反应炉石英管、传送器。石英件也是一中非常大的污染源,通常由散气与微粒的方式产生。即使是高纯度石英也含有许多重金属离子,这些离子可以从石英中散出进入扩散与氧化工艺反应的气流中,特别是在高温反应中。这些微粒来自晶圆与晶圆舟的擦伤和晶圆舟与反应炉石英的摩擦。(解决这个问题的方法将在第十一章中讨论)半导体业使用的石英一般是电子和焰熔工艺制造的。22

设备。 污染控制的成功与否与确认污染源是息息相关的。许多分析(图5.22)显示机械设备是最大的微粒污染源。到二十世纪九十年代为止,设备引发的微粒升至所有污染源的75%至90%,23但这并不意味机械设备变得越来越脏。由于对空气、化学品与生产人员污染的控制越来越先进,使得设备变为污染控制的焦点。缺陷产生率是设备生产规格的一部分。一般来讲,每片晶圆每次通过设备后增加的颗粒个数(ppp)是有详细说明的,并使用每片晶圆每次通过的颗粒增加数(PWP)这一术语。

图5.22微粒污染源.。这项1985年的研究显示设备产生的污染为最大敌人,见“SEMI”分析, 作者Dr. C. Rinn Cleavelin, Texas Instruments ( SEMI版权所有)

Wafer Fab Particulate Sources芯片加工厂微粒源

Equipment设备

Process工艺

People人员

Wafer Handling芯片操作

Static Charge静电

Chemical Purity化学品纯度

微粒产生率的降低要从设计方法与材料的选择入手,其他因素包括颗粒进入晶圆与沉积反应的机械装置的传播方法,例如静电。大多数设备是在与客户的晶圆制造厂相同洁净度的洁净室制造的。一组不同的工艺设备共享同一个洁净局部装卸空间可以降低使用多个装卸站所产生的污染。多反应室的设备将在第15章讨论。有一种趋势是在工艺反应室配备现场的微粒监视器,但对于这种级别的自动化和检测,困难是反应室内水平和晶圆表面水平相关性,探测器在大多数工艺反应室的恶劣和腐蚀环境中的使用寿命。

洁净室的物质与供给

除了工艺化学品以外,加工晶圆还需要大量的其他物质与供给。这些物品须满足洁净度要求。记录单、表格和笔记本都需要用无脱落表面的纸张或聚脂塑料制造。铅笔是不允许使用的,钢笔须是不能擦去字迹的。

晶圆储存盒是由特殊的不产生微粒的物质制造,运输车与反应管也是一样。车轮与设备不使用润滑油脂。在许多区域中,机械工具与工具箱要经过清洁,并存放在洁净室里。

洁净室的维护

洁净室的定期维护是非常必要的。清洁人员必须要穿着与生产人员一样的洁净服,洁净室的清洁器具,包括拖把,也要仔细选择。一般家庭使用的清洁器具太脏,无法在洁净室使用。而且使用真空吸尘器也要特别注意。在真空吸尘器中的排风系统中,装有HEPA过滤器,现在已经可以在洁净室中使用。许多洁净室有内置式真空系统来减少清洁时产生的脏东西。

擦净工艺工作台需要使用特殊的低污染的抹布与海绵。而且擦拭的程序也是非常关键的。墙面的擦拭要从上到下,桌面要从后向前。用喷壶喷洒的清洁剂,应喷到洁净布表面,而不是被清洁物表面。虽然这个方法很简单,但可以减少在晶圆与设备上的不必要的过量喷洒。这样洁净室的清洁本身也就成为支持半导体工艺的辅助技术。许多制造厂聘请外部认证公司24来确定洁净等级、工作过程、程序文件与控制程序,并加以文件化。

晶片表面清洗

洁净的晶片是芯片生产全过程中的基本要求,但并不是在每个高温下的操作前都必须进行。一般说来,全部工艺过程中的高达20%的步骤为晶片清洗。25在这里将要描述的清洗工艺,将贯穿芯片生产的全过程。

半导体工艺的发展过程在很多方面可以说是清洗工艺随着对无污染晶片需求不断增长而发展的过程。晶片表面有四大常见类型的污染,每一种在晶片上体现为不同的问题,并可用不同的工艺去除。这四种类型是:

1. 颗粒

2. 有机残余物

3. 无机残余物

4. 需要去除的氧化层

通常来说,一个晶片清洗的工艺或一系列的工艺,必须在去除晶片表面全部污染物(上述类型)的同时,不会刻蚀或损害晶片表面。它在生产配制上是安全的、经济的,是为业内可接受的。通常对清洗工艺的设计适用于两种基本的晶片状况。一种叫作前线(FEOL),特指那些形成活性电性部件之前的生产步骤。在这些步骤中,晶片表面尤其是MOS器件的栅区域,是暴露的、极易受损的。在这些清洗步骤中,一个极其关键的参数是表面粗糙度。过于粗糙的表面会改变器件的性能,损害器件上面沉积层的均匀性。表面粗糙度是以纳米为单位的表面纵向变差的平方根(nmRMS)。2000年的要求是0.15纳米,但到2010年要逐渐降低到0.1纳米以下。26在FEOL的清洗工艺中,另外一个值得关注的方面是光片表面的电性条件。器件表面的金属离子污染物改变电性特征,尤其是MOS传感器极易受损。Na+, 连同Fe, Ni, Cu 和Zn, 是典型的问题(见第四章)。清洗工艺必须将其浓度降至2.5x109原子/厘米2以下从而达到2010年的器件需要。铝和钙也是存在的问题,它们在晶片表面的含量需要低于5x109原子/厘米2的水平。27

另一个最为关键的方面是保持栅氧的完整性。清洗工艺可能会破坏栅氧从而使其粗糙,尤其是叫薄的栅氧最易受到损害。在MOS传感器中,栅氧是用来作绝缘介质的,因此它必须具有一致的结构,表面状态和厚度。栅氧的完整性是靠测试栅的电性短路来测量的。MRTS指明,在180纳米的长度上,用5毫伏/厘米的电压测试30秒钟,技术级栅显示的缺陷率必须低于0.02缺陷/平方厘米。28

对于BEOL(后线)的清洗,除了颗粒问题和金属离子的问题,通常的问题是阴离子、多晶硅栅的完整性、接触电阻、过孔的清洁程度、有机物以及在金属布线中总的短路和开路的数量。这些问题将在第13章中讨论。光刻胶的去除也是FEOL和BEOL都存在的很重要的一种清洗工艺。它所存在的问题将在第9章中探讨。

不同的化学物质与清洗方法相结合以适应工艺过程中特殊步骤的需要。典型的FEOL清洗工艺(例如氧化前的清洗)列在图5.23中。所列出的FEOL清洗称为非HF-结尾的工艺。其它的类型是以HF去除工艺收尾的清洗。非HF-结尾的表面是亲水性的,可以被烘干而不留任何水印,同时还会生成(在清洗过程中形成)一层薄的氧化膜从而对其产生保护作用。这样的表面也容易吸收较多的有机污染物。HF-结尾的表面是憎水性的,在有亲水性(氧化物)表面存在时不容易被烘干而不留水印。这样的表面由于氢的表面钝化作用而异常稳定。29对于HF-结尾或非HF-结尾的工艺的选择,取决于晶片表面正在制造的器件的敏感度和通常的对清洁程度的要求。第五章 污染控制--5

by r53858

颗粒去除

晶片表面的颗粒大小可由从非常大的(50微米)变化到小于一微米。大的颗粒可用传统的化学浸泡池和相应的清水冲洗除去。较小的颗粒被几种很强的力量吸附在表面所以很难除去。一种是范德华吸引力,这是一种在一个原子的电子和另一个原子的核之间形成的很强的原子间吸引力。尽量减小这种静电引力的技术是控制一种叫做z-电势的变量。z-电势是在颗粒周围的带电区与清洁液中带相反电荷的带电区域形成平衡的平衡电势。这个电势随着速度(当晶片在清洗池中移动时清洗液的相对移动速度),溶液的pH值和溶液中的电解质的浓度变化而变化的。同时,它还将受到清洗液中的添加剂,如表面活性剂的影响。我们可以通过设定这些条件来得到一个与晶片表面相同电性的较大电势,从而产生排斥作用使得颗粒从晶片表面脱落而保留在溶液中。

Capillary引力是另外一个问题。它产生了颗粒与表面之间形成的液体桥(图5.24)。Capillary引力可以比范德华引力大。30表面活性剂或一些机械的辅助,例如超声波,被用来去除表面的这些颗粒。

清洗工艺多为一系列的步骤,用来将大小不一的颗粒同时除去。最简单的颗粒去除工艺是用位于清洗台的手持氮气枪喷出的经过过滤的高压氮气吹晶片的表面。在存在小颗粒问题的制造区域,氮气枪上配置了离子化器,从而除去氮气流中的静电,而使晶片表面呈中性。氮气吹枪是手持的,操作员在使用它的时候必须注意不要污染操作台上的其它晶片或操作台本身。通常在洁净等级为1/10的洁净室中,不使用吹枪。

晶片刷洗器

晶片外延生长对于晶片清洁程度的严格要求导致了机械的晶片表面洗刷器的发展。同时这一方法也被用在非常关键的颗粒去除中。

刷洗器将晶片承载在一个旋转的真空吸盘上(图5.25)。在一般去离子水直接冲洗晶片表面的同时,一个旋转的刷子近距离地接触旋转的晶片。刷子和晶片旋转的结合在晶片表面产生了高能量的清洗动作。液体被迫进入晶片表面和刷子末端之间极小的空间,从而达到很大的速度,以辅助清洗。必须注意的是,要保持刷子和清洗液道路的清洁以防止第二污染。另外,刷子到晶片的距离要保持一定以防止在晶片表面造成划痕。

在去离子水中加入表面活性剂可以提高清洗的效果,同时防止静电的形成。在某些应用中,稀释的NH4OH被用作清洗液以防止在刷子上形成颗粒,同时控制系统中的Z-电势。31

刷洗器可以设计为有自动上/下料功能的独立的操作单位,也可以设计为其它设备的一部分,在工艺过程前自动执行对晶片的清洗。

高压水清洗

对由于静电作用附着的颗粒的去除首先成为玻璃和铬光刻掩膜板的清洗的必须。于是发展为高压水喷洒清洗。将一注小的水流施加2000~4000 PSI的压力,水流连续不断地掩膜或晶片的表面,除去大小不一的颗粒。在水流中经常加入少剂量的表面活性剂作为去静电剂。

有机残余物

有机残余物是含碳的化合物,例如指纹中的油分。这些残余物可以在溶剂浸泡池中被去除,例如丙酮,乙醇或TCE。一般说来,要想将晶片表面的溶剂完全烘干非常困难,所以如果可能,会尽量避免用溶剂清洗晶片。另外,溶剂经常会有杂质,从而使其本身成为了污染源。

无机残余物

无机残余物是那些不含碳的物质。这样的例子有无机酸,如盐酸,氢氟酸。它们会在晶片制造的其它工序中介绍。关于晶片表面有机物和无机物的去除,有一系列的清洗方案,将在下面的部分介绍。

化学清洗方案

半导体工业中存在大范围的清洗工艺。每个制造区域对于清洁度有着不同的需要,也对不同的清洁方案有着不同的经验。在这一节中描述的清洗方案是那些最常用的类型。当然,在不同的晶片制造区域,它们又将有多种变化或是方案的多种不同组合。在这里描述的是在掺杂,沉积和金属沉积前晶片的清洗工艺。(光刻胶的去除这一特例会在第8章中讲解)

液体的化学清洗工艺通常称为湿法工艺或湿法清洗。浸泡型清洗在嵌入清洗台的台板上的玻璃,石英或是聚四氟乙烯的池子中进行(见第4章)如果一种清洗液需要加热,那么池子会座落在一个加热盘上,周围被加热用的电阻线缠绕或者其内部有一个浸入式加热器。化学品也可用于喷洒,应用于直接冲击或离心分离设备中(见旋转清洗烘干机)。

常见的化学清洗

硫酸。一种常见的清洗溶液是热硫酸添加氧化剂。它也是一种通常的光刻胶去除剂(见第8章)。在90~125 OC的范围中,硫酸是一种非常有效的清洗剂。在这样的温度下,它可以去除晶片表面大多数无机残余物和颗粒。添加到硫酸中的氧化剂用来去除含碳的残余物,化学反应将碳转化成二氧化碳,后者以气体的形式离开反应池:

C + O2 à CO2 (气体)

一般使用的氧化剂有:

过氧化氢(H2O2),亚硫酸氨 [(NH4)2S2O8],硝酸(HNO3),和臭氧(O3)

硫酸和过氧化氢。过氧化氢和硫酸混合制成一种常见的清洗液,用于各个工艺过程之前,尤其是炉工艺之前晶片的清洗。它也可用作光刻操作中光刻胶的去除剂。在业内,这种配方有多种命名,包括Carro’酸和Piranha刻蚀(Piranha是一种非洲的食人鱼)。后者证明了这种溶液的进攻性和有效性。

一种手动的方法是在盛有常温的硫酸容器中加入30%(体积)的过氧化氢。在这一比例下,发生大量的放热反应,使容器的温度迅速地升到了110~130OC的范围。随着时间发展,反应逐渐变慢,反应池的温度也降到有效范围内。这时,往反应池中添加额外的过氧化氢或者不再添加。往反应池中不断添加最终会导致清洗效率降低。这是因为过氧化氢转化为水,从而使硫酸稀释。

在自动的系统中,硫酸被加热到有效清洗的温度范围内。在清洗每一批晶片前,再加入少量(50~100毫升)的过氧化氢。这种方法保证清洁池处于合理的温度下,同时由过氧化氢产生的水可通过气化离开溶液。基于经济和工艺控制因素的考虑,一般选用加热硫酸这一方法。这种方法也使两种化学物质的混合比较容易自动实现。

臭氧。 氧化剂添加剂的作用是给溶液提供额外的氧。有些公司将臭氧的气源直接通入硫酸的容器。臭氧和去离子水混合是一种去除轻微的有机物污染的方法。32典型的工艺是将1~2 ppm 的臭氧通入去离子水中,在室温下持续10分钟。33

氧化层的去除

我们已经提及了硅片氧化的容易程度。氧化反应可以在空气中发生,或者是在有氧存在的加热的化学品清洗池中。通常在清洗池中生成的氧化物,尽管薄(100~200Å),但其厚度足以阻止晶片表面在其它的工艺过程中发生正常的反应。这一薄层的氧化物可成为绝缘体,从而阻挡晶片表面与导电的金属层之间良好的电性接触。

去除这些薄的氧化层是很多工艺的需要。有一层氧化物的硅片表面叫做具有吸湿性。没有氧化物的表面叫做具有憎水性。氢氟酸是去除氧化物的首选酸。在初始氧化之前,当晶片表面只有硅时,将其放入盛有最强的氢氟酸(49%)的池中清洗。氢氟酸将氧化物去除,却不刻蚀硅片。

在以后的工艺中,当晶片表面覆盖着之前生成的氧化物时,用水和氢氟酸的混合溶液可将圆形的孔隙中的薄氧化层去除。这些溶液的强度从100:1到10:7(H2O:HF)变化。对于强度的选择依赖于晶片上氧化物的多少,因为水和氢氟酸的溶液既可晶片上孔中的氧化物刻蚀掉,又可将表面其余部分的氧化物去除。既要保证将孔中的氧化物去除,同时又不会过分地刻蚀其它的氧化层,就要选择一定的强度。典型的稀释溶液是1:50到1:100。

如何处理硅片表面的化学物质是一直以来清洗工艺所面临的挑战。一般地,栅氧化前的清洗用稀释的氢氟酸溶液,并将其作为最后一步化学品的清洗。这叫做HF-结尾。HF-结尾的表面是憎水性的,同时对低量的金属污染是钝化的。然而,憎水性的表面不轻易被烘干,经常残留水印。34另一个问题是增强了颗粒的附着,而且还会使电镀层脱离表面。35

RCA清洗。在二十世纪六十年代中,Warner Kern,一名RCA公司的工程师,开发出了一种两步的清洗工艺以去除晶片表面的有机和无机残留物。这一工艺被证明非常有效,而它的配方也以简单的“RCA清洗”为人们熟知。只要提到RCA清洗,就意味着过氧化氢与酸或碱同时使用。第一步,标准清洗-1(SC-1)应用水,过氧化氢和氨水的混合溶液的组成,从5:1:1到7:2:1变化,加热温度在75~85OC之间。SC-1去除有机残余物,并同时建立一种从晶片表面吸附痕量金属的条件。在工艺过程中,一层氧化膜不断形成又分解。

标准清洗-2(SC-2)应用水,过氧化氢和盐酸,按照6:1:1到8:2:1的比例混合的溶液,其工作温度为75~85 OC之间。SC-2去除碱金属离子,氢氧根及复杂的残余金属。它会在晶片表面留下一层保护性的氧化物。化学溶液的原始浓度及其稀释的混合液均列在图5.26中。

多年来,RCA的配方被证实是经久不衰的,至今仍是大多数炉前清洗的基本清洗工艺。随着工业清洗的需求,化学品的纯度也在不断地进行改进。根据不同的应用,SC-1和SC-2前后顺序也可颠倒。如果晶片表面不允许有氧化物存在,则需加入氢氟酸清洗这一步。它可以放在SC-1和SC-2之前进行,或者在两者之间,或者在RCS清洗之后。

在最初的清洗配方的基础上,曾有过多种改进和变化。晶片表面金属离子的去除曾是一个问题。这些离子存在于化学品中,并且不溶于大多数的清洗和刻蚀液中。通过加入一种整合剂,例如ethylenediamine-tetra-acetic酸,使其与这些离子结合,从而阻止它们再次沉积到晶片上。

稀释的RCA溶液被发现具有更多的用途。SC-1稀释液的比例为1:1:50(而不是1:1:5),SC-2的稀释液的比例为1:1:60(而不是1:1:6)。这些溶液被证明具有与比它们更浓的溶液配方同样的清洗效果。而且,它们产生较小的微观上的粗糙,节约成本,同时容易去除。36

室温和氧化的化学物质

理想的清洗工艺是应用那些完全安全、易于并比较经济地进行处理的化学品,并且在室温下进行。这种工艺并不存在。然而,关于室温下化学反应的研究正在进行。其中一种37是将臭氧与另外两种浓度的氢氟酸溶液(图5.27)在室温下注入盛有超纯净水的清洗池。超声波作为辅助以提高清洗的有效性。

喷洒清洗。标准的清洗技术是浸泡在湿法清洗台或全自动机器中的化学池中进行的。当湿法清洗被应用到0.35到0.50微米的技术时代时,也相应出现了一些顾虑。化学品越来越多,浸泡在池中会导致污染物的再次沉积,而且晶片表面越来越小,越来越深的图形阻碍了清洗的有效性。多样的清洗方法于是开始结合。喷洒清洗具有几个优越性。化学品直接喷到晶片表面而无需在池中保持大量的贮备,导致化学品的成本降低。化学品用量的减少也使得处理和除去运化学废物的花费降低。清洗效果也有所提高。喷洒的压力有助于清洗晶片表面带有深孔的很小的图形。而且,再次污染的机率也变小。喷洒的方法由于晶片每次接触的都是新鲜的化学品,使允许清洗后立即进行清水冲淋,而无需移至另外的一个清水冲洗台上进行。

干法清洗。关于湿法浸泡方法的考虑拒绝了对于气相清洗的想法和发展。对于清洗,晶片暴露在清洗液或刻蚀液的蒸汽中。氢氟酸/水的混合蒸汽经证实可用来去除氧化物,以过氧化物为基础的清洗液的气相取代物也有存在。38

这一工业最终的梦想是完全的干法清洗和干法刻蚀。目前,干法刻蚀(等离子体,见第9章)已经很完善得建立起来。干法清洗正在发展之中。紫外臭氧可以氧化并光学分离晶片表面形成的污染物。

低温清洗。 高压的二氧化碳 CO2,或雪清洗,是一种新兴的技术。(图5.28)CO2从一个喷嘴中直接喷到晶片表面。当气体从喷嘴中喷出时,其压力下降从而导致快速冷却,然后形成CO2 颗粒,或叫雪花。相互撞击的颗粒的压力驱散表面的颗粒并由气流将其携带走。表面的物理撞击提供了一种清洗作用。氩气的喷雾是另外一种低温清洗。氩气相对较重。它的较大的原子在压力下直喷到晶片表面可以除去颗粒。

一种结合了氧气和氩气的综合的方法,称为Cryokinetic。在压力下将气体预冷使其形成液气混合物并流入一个真空反应室中。在反应室中,液体迅速膨胀形成极微小的结晶将颗粒从晶片表面击走。39

水的冲洗

每一步湿法清洗的后面都跟着一点去离子水的冲洗。清水冲洗具有从表面上去除化学清洗液和终止氧化物的刻蚀反应的双重功效。冲洗可用几种不同的方法来实现。未来的焦点集聚在提高冲洗效果和减少水的用量上。1997年的NTRS声称,到2010年争取实现在尺寸为50纳米的器件上(水用量由目前的30 加仑/每平方英寸硅片减少到2加仑/每平方英寸硅片)。每平方英寸硅片的水用量由目前的30 加仑减少到2010年的2 加仑。

溢流式清洗器。自动的表面清洗并不是单独地将晶片浸泡在—池水中。完全的彻底的冲洗需要晶片表面有清洗的水不断地流过。其中一种方法叫溢流式清洗器。(图 5.29)它通常是嵌入清洗台面板内的一个池子。去离子水从盒子的底部进入从晶片周围流过,再经过一个闸门从排水系统排出。从下部的底盘进入冲洗器的一般氮气的气泡加强了流水的冲洗作用。由于氮气的气泡从水中从下向上通过,有助于晶片表面化学品和水的混合。这一类型称为气泡式。另一不同类型为平行式下流冲洗器。在这一设计中,水从冲洗池外部进入竖直向下流过晶片。(图 5.30)

由经验得出的法则是,充分的冲洗要以流速为每分钟等于冲洗池体积的五倍的流量(每分钟的水更换次数)持续冲洗至少5分钟(取决于晶片的直径)。如果冲洗池的体积为32,则流量应至少为15升/分钟。

冲洗的时间长短是由测量排出冲洗池的水的电阻率决定的。化学清洗液在冲洗的水中是带电的分子,它们的存在可由水的电阻率推知。如果进入冲洗池的水的电阻为18MΩ 的水平,那么在清洗池的出口处水的电阻为15到18兆欧时说明晶片已经清洗并冲淋干净。由于清水冲洗至关重要,所以通常至少要进行两种冲洗,而总共的冲洗时间要设定为由电阻率测量而确定的最小冲洗时间的2到5倍。通常在冲洗池出口处安装一个水电阻率测量表以不断地测量出口处水的电阻率,并在冲洗完成时给出信号。

喷洒式冲洗 。 流动的水通过稀释的机械原理将晶片表面水溶性的化学物质除去。最表层的化学物质溶解于水并被水流携带走。这种动作在一次一次不间断地进行。较快的水的流速可以更快地将化学物质溶解从而使冲洗速度提高。水的更换次数直接决定了冲洗的速度。这可以通过想象以一个非常快的水流速度在一个非常大的冲洗池中进行的冲洗来理解。从晶片表面去除掉的化学物质会均匀地分布在冲洗池中因此一部分也将仍然会附着在晶片表面。只有通过足够多的水流进和并携带着化学物质流出冲洗池,才可将化学物质最终从池中排出。

另一种冲淋速度较快的方法是利用水喷淋的方法。喷洒是通过来自它自身的动量的物理作用除去化学物质的。那些大量的小水滴冲击晶片表面,可以达到与更换率极高的冲洗相同的效力。除了更有效的冲洗效果与溢流式冲洗相比喷洒冲洗的用水量相当少。但当用电阻率监测器测量喷洒冲洗器中排出的水的电阻时,一个问题随之而来。被喷射的水捕捉到的空气中的二氧化碳相当于带电的颗粒,从而被电阻率测量器视为污染物,而其实它们并不是。

排放式冲洗。考虑到冲洗的有效性和水用量的节约,排放式冲洗无疑是一个引人注目的方法。系统的构成类似溢流式冲洗,但具有喷洒能力。晶片被放量到干的冲洗槽中即刻被去离子水喷淋。当喷淋进行时,冲洗槽被水迅速地充满。当水溢流至冲洗槽的顶端,其底部的一个活门swings 开启,将水顷刻间排入排放系统。这样的填满和排放的过程反复几次直至晶片被完全冲洗干净。

排放式冲洗的另一个好处是全部过程在一个槽中进行,节约设备和空间。它还是一个可以自动操作用系统,操作员只需将晶片放入槽中(这一操作也可自动实现)然后按下启动键。

超声波辅助进行的清洗和水冲洗。在化学品清洗池或水冲洗系统中的额外的超声波振动有助于并可加速湿法工艺的进行。使用超声波可以提高清洗效力从而允许较低的槽温。超声波是由清洗槽外部安装的变频器产生的能量波。通常使用两个波段。在20000—50000赫兹(1赫兹(Hz)=1周/秒)范围的叫超声波,在850千赫(KHz)范围的叫兆声波。40超声波是通过蒸气旋涡来辅助冲洗的。振动在液体中形成极微小的气泡而这些气泡快速地崩溃而产生极微小的擦洗的动作从而除去颗粒。这一现象称为气涡。兆声波的辅助作用是通过另外一种机理来实现的。依据流体力学,固体表面与液体之间有一个静止或缓慢移动的界面,例如晶片的表面。小的颗粒可被保持在这层界面中而不会接触化学清洗液。兆声波的能量可以消除这一界面,从而使颗粒得以清洗。另外,一种叫做声流的现象使得水或清洗液流过晶片的速度加快,从而提高清洗效率。41

旋转淋洗烘干机(SRDs)。 清水冲洗后,必须将晶片烘干。这并不是一个无关紧要的过程。任何保留在晶片表面的水(甚至是原子)都可能对以后的任何一步操作产生潜在的影响。目前所应用的有三种烘干技术(之间有所不同)。

烘干技术

**旋转淋洗烘干机

**异丙醇(IPA)蒸汽烘干法

**表面张力/麦兰烘干法。

完全的烘干是在一个类似离心分离机的设备中完成的。一种方式是将晶片承载器装入一圆筒状容器内部的片匣固充器中。在这一圆筒状容器的中心是一排连接着去离子水和热氮气的带孔的管子。(图5.33)

烘干的过程实际起始于晶片的冲洗,因为晶片是围绕着喷水的中心管柱旋转的。然后,当热氮气从中心管柱中喷出时,SRD转换为高速旋转。不难想象,旋转把水从晶片表面甩掉。热氮气可帮助去除紧附于晶片上的小的水珠。

SRDS还可以设计用来做单个晶片承载器的烘干。承载器可以被滑动推入反应室内部的一个旋转固定器中。水和氮气从其侧壁进入反应室而不是通过一个位中心的管柱。冲洗和烘干是在承载器绕其自身的轴线旋转时进行的。这种类型的SRD称为轴线烘干机。这两种烘干机均被应用于全自动的晶片清洗和刻蚀工艺。作为晶片清洗机,其所需的化学品通过管道连接到机器上,又由用(微处理机)控制的阀门将正确的化学品输送到反应室中。

异丙醇(IPA)蒸气烘干法。 一个近来又被重新发现的烘干技术是醇类烘干法。(图5.34)在烘干器的底部有一个液体IPA的贮液罐。其上部充满蒸气(气相)。当一片表面带水的芯片悬置于蒸气中时,IPA将芯片表面的水取代。IPA蒸气区域周围的冷却管使IPA蒸气中的水蒸汽凝结从而除去芯片表面的水。另一种为直接取代型气相烘干机。这一系统中,芯片被直接从水池中拿出放入IPA蒸气中,IPA对水的取代在其中发生。

表面张力/麦兰(marangoni)烘干。当芯片从水中被慢慢拿出水面时,水的表面张力产生一种特殊条件。张力吸走表面的水,使芯片变干。一种有机物, 如IPA 或N2的气流在芯片和水的界面的出现,将使上述效果增强。IPA/N2的气流产生一种表面张力梯度从而使得芯片上的水从其表面流入水中。这一内部流动进一步加强了芯片去水的效果。在实际应用中,芯片会被从水池中拿出,或者冲洗池中的水会慢慢下降使芯片露出水面。

第五章 污染控制--6

污染检测/总结

对各种污染形式的检测在第八章和第十四章中具体描述。表5.35总结了有关洁净室洁净度的规范。

Year of Production 2001 2006 2012

-------------------------------------------------------------------------------------------------------

Line width (nm) 150 100 50

-------------------------------------------------------------------------------------------------------

Air Critical Particle Size (nm) 8 2 1

-------------------------------------------------------------------------------------------------------

Water oxidizable carbon (ppb) 1 <1 <1

-------------------------------------------------------------------------------------------------------

Water Dissolved Oxygen (ppb) 1-10 1 1

-------------------------------------------------------------------------------------------------------

Water Particle>critical size <0.2 per ml <0.2 per ml <0.2 per ml

-------------------------------------------------------------------------------------------------------

Liquid Particles>critical size <0.5 per ml <0.5 per ml <0.5 per ml

-------------------------------------------------------------------------------------------------------

HCl, H2O impurities (ppt) <1000 <1000 <1000

-------------------------------------------------------------------------------------------------------

BEOL solvents K, Li, Na (ppt each) <1000 <1000 <1000

-------------------------------------------------------------------------------------------------------

POU Gases particles (per liter) 2 2 2

表5.35 SIA Roadmap Projections (Micro October 1998 p.54)

关键概念及术语

浮质 可移动的离子污染物

风淋 微粒

前厅 工艺用气体

细菌 湿法工艺化学品

洁净室洁净等级 服务室

洁净室设计 温度,湿度,烟雾

污染源 全面的洁净室规划策略

去离子水 隧道策略

洁净服要求 纵向层狀气流

高效微粒空气过滤器 (HEPA) 超低频工作站(VLF)

微米 小型环境

低温清洗 臭氧清洗

芯片清洗技术 芯片清洗用化学品

第六章 工艺良品率-1

概述

高水平的工艺良品率是生产性能可靠的芯片并获得收益的关键所在。本章将结合影响良品率的主要工艺及材料要素对主要的良品率测量点做出阐述。对于不同电路规模和良品率测量点的典型良品率也在本章中列出。

目的

完成本章后将能够:

1,指出三个工艺良品率的主要测量点

2,解释晶圆直径,芯片尺寸,芯片密度,边缘芯片数量和制程缺陷密度对晶圆电测良品率的影响

3,通过单步工艺制程良品率来计算出累积晶圆生产良率

4,解释及计算整体工艺良品率

5,对影响制造良品率的4个主要方面做出解释

6,建立良品率相对时间的曲线来反映不同的工艺和电路成熟程度

7,解释高水平工艺良品率和器件可靠性之间的联系

6.1 良品率测量点

维持及提高良品率(yield)对半导体工业至关重要。任何对半导体工业做过些许了解的人都会发现,整个工业对其生产良率及其关注。的确如此,半导体制造工艺的复杂性,以及生产一个完整的封装器件所需要经历的庞大工艺制程数量,使导致这种对良品率超乎寻常关注的基本原因。这两个方面的原因使得通常只有20%~80%的芯片能够完成晶圆生产全过程,成为成品出货。

对于大部分的制造工程师来说,这样的良品率看上去真是太低了。可是当我们考虑一下所面临的挑战,是要在极其苛刻的洁净空间中,在1/2平方英寸的芯片范围内,制作出数百万个微米量级的元器件平面构造和立体层次,就会觉得能够生产出任何这样的芯片已经是半导体工业了不起的成就了。

另外一个抑制良品率的重要方面是大多数生产缺陷的不可修复性。不像有缺陷的汽车零件可以更换,这样的机会对半导体制造来说通常是不存在的。缺陷芯片或晶圆一般是无法修复的。在某些情况下没有满足性能要求的芯片可以被降级处理作低端应用。废弃的晶圆或许可以发挥余热,被用作某些工艺的控制晶圆(control wafer)或假片(dummy wafer) (参见6.5.1小节及第七章中关于氧化工艺的讨论)。

除了以上这些工艺方面的因素外,规模化的量产也使得良品率越发重要。巨额的资金投入,高于工业界平均比例的工程技术人员的使用,这些导致半导体生产高昂的分摊成本。居高不下的分摊成本,加上激烈竞争使得产品价格持续下滑,驱使大部分芯片生产厂运作在一个大规模量产,高良品率的水平上。

基于所有这些原因,也就不难理解半导体工业界对于良品率的执著了。大部分的设备和原材料供应商都以自己的产品可能提升良率来作为推销手段。同样,工艺工程部门也把维持和提高制程良率当作本部门的主要责任。良率在制程的每一站都回被计算出来,其中,3个主要良率被用来监控整个半导体工艺制程(参见图6.1)。

图6.1主要良率测量点

生产工序 测量内容

晶圆生产部门的良率=晶圆产出数/晶圆投入数

晶圆电测的良率= 合格芯片数/晶圆上的芯片总数

封装的良率= 终测合格的封装芯片数/投入封装生产线的合格芯片数

6.2 累积晶圆生产良品率

在晶圆完成所有的生产工艺后,第一个主要良品率被计算出来了。对此良品率有多种不同的叫法,如Fab良率(Fab Yield)、生产线良率、累积晶圆厂良率或CUM良率。

晶圆厂CUM良率用一个百分比来表示,可通过两种不同的计算方法得到。一种是用完成生产的晶圆总数除以总投入片数。这种简单的计算方法在实际上很少被使用。因为大部分的晶圆生产线同时生产多种不同类型的电路。不同类型的电路有不同的特征工艺尺寸和密度参数。一条晶圆生产线经常是生产一系列不同的产品,每一种产品都有其各自不同数量的工艺步骤和难度水平。在这种情况下,将会针对每一类产品计算一个合成良率。

一条晶圆生产线上会存在有大量制程中的晶圆,这些晶圆的生产周期从4~6周不等。一类或更多类产品在制程中的某些地方受阻滞留,这种情况并非罕见。完成制程的晶圆很少与投入的警员直接对应。因此只是简单地使用投入与产出的晶圆数很难反映每一种类型电路的真实良率。

要得到CUM良率,需要首先计算各制程站良率(station yield),即以离开单一制程站的晶圆数进入此制程的晶圆数:

制程站良率=离开制程站晶圆数/进入制程站晶圆数

将各制程站良率依次相乘就可以得到整体的晶圆生产CUM良率:

晶圆生产CUM良率=良率(station-1)*良率(station-2)*...*良率(station-N)

图6.2列出了一个11步的晶圆工艺制程,与我们第5章中使用的方法一样。

No. 工艺步骤 晶圆进 良率 晶圆出 累积良率

1 场氧化物 1000 99.5 995 99.5

2 S/D光刻 995 99.0 985 98.5

3 S/D掺杂 985 99.3 978 97.8

4 栅极区光刻 978 99.0 968 96.8

5 栅极氧化 968 99.5 964 96.4

6 接触孔光刻 964 94.0 906 90.6

7 金属层沉积 906 99.2 899 89.9

8 金属层光刻 899 97.5 876 87.6

9 合金属层 876 100 976 87.6

10 钝化层沉积 876 99.5 872 87.2

11 钝化层光刻 872 98.5 859 85.9

*所列良率数值为特定工艺的典型数值

图6.2 累积(晶圆生产)良率计算

典型的晶圆生产CUM良率在50%到95%之间,取决于一系列的因素,我们接下来对此会做详细讨论.计算机出来的CUM良率被用于计划生产,或被工程部门和管理者作为工艺有效性的一个指标.

6.3 晶圆生产良率的制约因素

晶圆生产良率受到多方面的制约.下面列出了5个制约良率的基本因素,任何晶圆生产厂都会对他们进行严格的控制.这5个基本因素的共同作用决定了一个工厂的综合良率.

1.工艺制程步骤的数量

2.晶圆破碎和弯曲

3.工艺制程变异

4.工艺制程缺陷

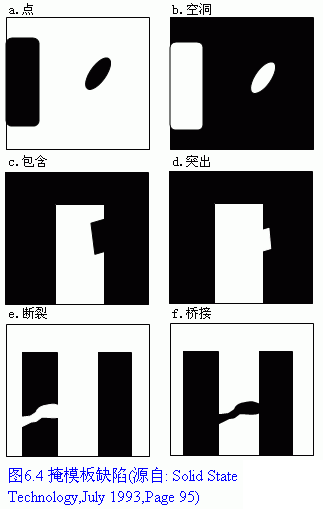

5.光刻掩模板缺陷

6.3.1 工艺制程步骤的数量

从图6.2中看出,要得到85.9%的CUM晶圆生产良率,每个单一制程站良率必须高于90%.图所示只是一个非常简单的11步工艺流程.ULSI电路需要50~100个主要工艺操作.到2010年,生产晶圆的主要工艺操作将达到600个.每个主要工艺操作包含几个步骤,每个步骤又依序涉及到几个分步.能够在经过如此众多的工艺步骤后仍然维持很高的CUM良率,这一切显然应归功于晶圆生产厂内持续不断的良率压力.在如此众多的工艺步骤作用下,电路本身越复杂,预期的CUM良率也就会越低.

工艺步骤的增加同时提高了另外4个制约良率因素对制程中晶圆产生影响的可能性.这种情况是所谓的数量专治.例如,要想在一个50步的工艺流程上获得75%的累积良率,每单步的良率必须达到99.4%!专治在此类计算中更进一步表现为CUM良率决不会超过各单步的最低良率.如果一个工艺制程步骤只能达到50%的良率,整理的CUM良率不会超过50%.

每个主要工艺操作都包含了许多工艺步骤及分步,这使得晶圆生产部门面临着曰益升高的压力.在图示的11步工艺流程中,第一步是一个氧化工艺.一个简单的氧化工艺需要完成几个工艺步骤.他们是:清洗、氧化和评估。它们每一步度包含有分步骤。图6.3中列出了一个典型的氧化清洗工艺所包含的6个分步骤。每一个步骤都存在污染晶圆、打碎晶圆、或者犯其他错误的机会。

图6.3 氧化工艺的分步骤

对于商用半导体来说,75%的晶圆厂CUM良率是赚取利润的底线,自动化生产线则要达到90%或以上的良率。

6.3.2 晶圆破碎和弯曲

在晶圆生产过程中,晶圆本身会通过很多次的手工和自动的操作.每一次操作都存在将这些晶圆打破的可能性.设想一下一片典型6寸晶圆的厚度只有大约2.5%英寸.操作员需要具有小心操作晶圆的技巧,自动化的操作台必须被维护在良好的状态以使晶圆被打碎的可能性减为最小.

对晶圆的多次热处理使得晶圆更容易破裂.热处理造成晶格结构上的损伤导致晶圆在后续步骤中增加了破碎的机会.在一个手动的工艺制程中,还有机会对一片破碎的晶圆进行后续生产.可是自动化的生产设备只能处理完整的晶圆.因此,如果破碎,不论破碎大小,整片晶圆都将被拒收并丢弃.

如果操作得当,硅晶圆相对而言易于操作,并且自动化的设备已经把晶圆的破碎降到了一个很低的水平.但是砷化镓晶圆就没有这么好的弹性,晶圆破碎是限制其良率的主要因素.由于砷化镓电路和器件具有很高的性能和高昂的价格,所以在砷化镓生产线上,对破碎晶圆的继续生产是可能的,特别是通过手动的工艺.

在尽量减少晶圆破碎的同时,晶圆的表面在整个生产过程中必须保持平整.这一点对于使用光刻技术将电路图案投射到晶圆表面的晶圆生产至关重要.如果晶圆表面弯曲或起伏不定,投射到晶圆表面的图像会扭曲变形,并且图像尺寸会超出工艺标准.晶圆的弯曲主要归因于晶圆在反应管中的快速加热/冷却(第七章将阐述对这一问题的解决方案).

6.3.3 工艺制程变异

在晶圆通过生产的各个工艺制程时,它会接受许多的掺杂,增层及光刻工艺制程,每一步都必须达到极其严格的物理特性和洁净度的要求.但是,即使是最成熟的工艺制程也存在不同晶圆之间,不同工艺之间,以及不同天之间的变化.偶尔某个工艺制程还会超出它的制程界限并生产出不符合工艺标准的晶圆.工艺制程的自动化所带来的最大好处就是将这种工艺制程变异减至最小.

工艺制程和工艺控制程序的目标不仅仅是保持每一个工艺操作在控制界限范围之内,更重要的是维持相应的工艺参数稳定不变的分布.大多数的工艺制程都呈现为一个在数学上称为正态分布( Normal Distribution) 的参数分布.本书将在第15章中对这个分布进行解释.这种分布也被称为中心极限分布(central theorem distribution), 它的特点是大部分的数据点处于均值附近,距离均值越远,数据点越少.有时一个工艺制程的数据点都落在指定的界限内,但是大部分的数据都偏向一端.表面上看这个工艺还是符合工艺界限,但是工艺数据分布已经改变了,很可能会导致最终形成的电路在性能上发生变化,导致达不到标准要求.晶圆生产的挑战性也就在于要保持各道工艺制程数据分布的持续稳定.

在整个晶圆生产工艺流程中,设有许多用来发现有害变异的检查和测试,以及针对工艺标准的周期性设备的参数校准.这些检测一部分由生产部门人员来执行,一部分由质量控制部门来执行.所有的这些检测以及工艺制程标准允许一定程度的变异.