刻蚀极致工艺——光刻(烧脑篇)

转自:微信公众号 显示汇,微信号Display_Sea

光刻机分为紫外光源(UV)、深紫外光源(DUV)、极紫外光源(EUV)。按照发展轨迹,最早的光刻机光源即为汞灯产生的紫外光源(UV)。之后行业领域内采用准分子激光的深紫外光源(DUV),将波长进一步缩小到ArF的193 nm。由于遇到了技术发展障碍,ArF加浸入技术成为主流。

想当年整个芯片工业,各家包括intel ,GF, 台积电,三星都在三星都在22nm,28nm这个节点卡了很久,想必是遇到193nm ArF的极限了。

然而193nm能做出50nm以下,1/4波长的尺度,已经非常神奇了不是吗?

不过这背后也存在命名问题。xx nm节点不意味着真正的结构就那么小。首先这个数字原来是指结构的half pitch,即一半的周期。而到了后来水份更多,一般是指最小feature-size。比如一排100nm周期的突起或者凹陷,突起的宽度20nm, 空隙80nm,那么不严格的说这也是一个20nm的工艺。

为什么193nm的ArF光能做出28nm的线?

1、利用光刻胶特性

单从光场分布来说,一个峰或谷的宽度很可能还是突破不了衍射极限。但是可以利用光刻胶的性质!

光刻胶曝光后的溶解性依赖于曝光量,这大家都知道,但是这个依赖很不线性。通过控制这种不线性,使得在某个阈值曝光量附近,小一点的完全不会溶解,大一点的极易被溶解,那通过准确把握曝光量,就可以轻松控制最小结构的线宽。

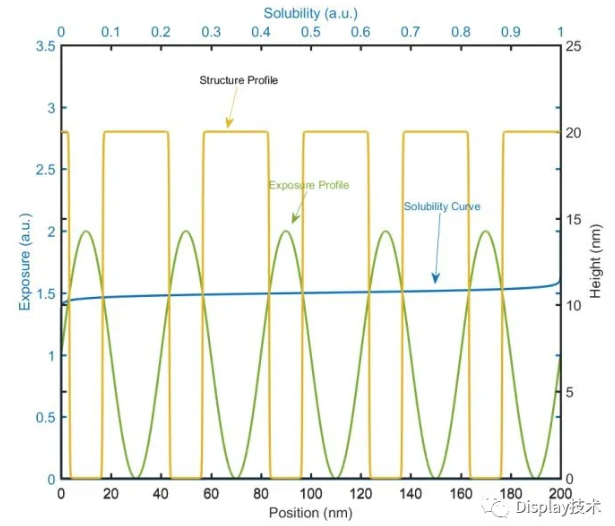

试想一个均匀分布类似正弦波的光场,把曝光将控制到只有波峰附近那些位置能完全溶解,之外的部分溶解性不变,那么最后做出来的结构就是一个周期和正弦波一样,但是最小宽度小的多的结构。

见下图。黄色曲线代表的结构的凹陷要小于光场分布一个峰的宽度。

当然这种方法也不是能做出无限小的Feature。毕竟光刻胶的溶解特性哪儿有想要什么就有什么的,每一种配方的研制都非常复杂,还要和现有的流程工艺匹配。而且光刻胶涂层毕竟是有厚度的,表面的曝光分布和整体也不尽相同。同时它的机械性质也无法维持很窄的细节的完整性。

还有另外一些方法能将光刻胶层被激活的区域集中在比曝光光场小很多的尺度内,包括各种玄乎的化学处理,热处理等。

2、SADP多次曝光工艺(LELE、LFLE)

既然有了上述方法,能让Minimum Feature Size至少小于半周期,那么接下来实现密度的增长就有了可能——通过多次曝光。

同样的结构,平移一下再做一遍就多了一倍的密度。

但是实施起来并没有那么简单。

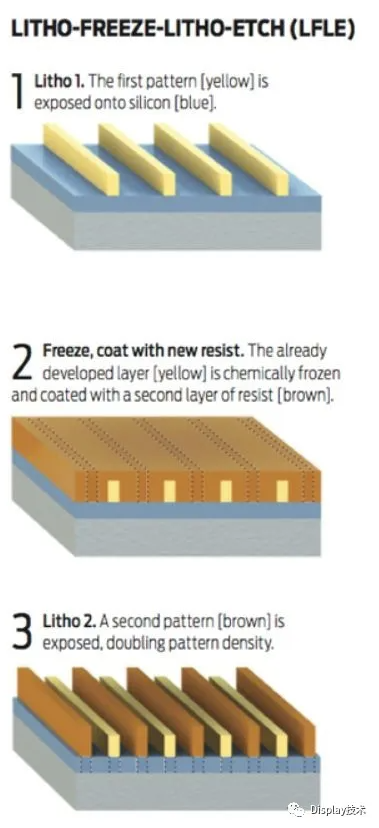

关键就是在后续曝光中要做到一个对先前结构保护冻结的步骤。最朴素的多重曝光技术就是,做一次,再做一次,可以称作LELE(Litho-Etch-Litho_Etch)。如下图

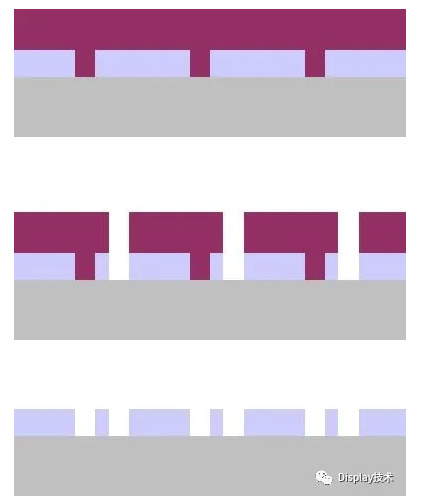

最上面是已经经过一次Patterning的保护层(藕荷色,如SiN)再加上一层光刻胶(紫色)。光刻胶在新的Mask下被刻出另一组凹槽(中间)。最后光刻胶层被去掉,留下可以进一步蚀刻的结构(下图)。

另外一个变种是Litho-Freeze-Litho-Etch (LFLE).