如何查Vt shift的Case?MOSFET开启电压(Vt)的制程因素!(转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

很久没有写文章了,客观原因是电脑坏了,主观原因是不知道写什么。类似我们的学习,我们很想好好学习,很想像某人一样功成名就,每个人都是上进的,科学的方法和明确的计划才是最重要的。看来我的反思如何把《芯苑》走的更远,希望大家能够给我些建议,我自己蠢就得求助你们!

好了,先把今天的课题讲完吧,前面很长一段时间都在讲栅极 (栅极材料以及介质),这些直接决定了MOSFET的开启电压,也是MOSFET的心脏。可是我们今天就反过来讲讲这个开启电压到底有那些制程因素影响?实际process过程中,我们要如何查找Vt shift的case?

开启电压,先讲讲这个东西怎么测的吧?我这个人还是喜欢从理论研究起,这样后面讲的东西比较不会显得轻浮枯燥。前面我们已经讲过MOSFET的原理就是在栅极加电压,通过GOX耦合作用在下面的沟道区反型(inversion)形成沟道使得源漏导通,很自然的定型的理解:开启电压就是让沟道反型,连接源漏区。那什么时候算开启?稍稍漏电流就算?还是完全开启才算?这就是Vt的测试标准。

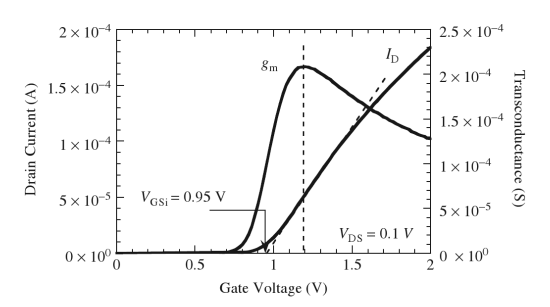

业界有两种电压测试方法,一种叫做1uA法(constant current),就是在Drain加0.1V,sweep gate,直到drain有0.1uA时候下的Vg就是Vt,这个方法现在很少用了,都是早期low technology时候用。现在都普遍采用第二种方法来测试了,叫做最大跨导法(Gmmax),或者土话叫外插法(Linear Extrapolation)。行业标准是:ASTM F617‑86。它的测试方法是:Drain加0.1V,Vb=Vs=0V,扫描Vg。画出Id-Vg曲线,并且在Id-Vg曲线上再画出跨到(Gm)曲线,也就是电流Id对Vg求导的曲线。找到Gm曲线的最大点与Id-Vg曲线的交叉点做切线与X轴交点(Vg'),然后再用Vg'减去1/2Vdd就是Vt了。很复杂吧?还是对着图边看边理解吧。(PMOS全部加一个负电压即可)

好了,勤学好问的人来了。为什么drain要0.1V?为什么要GmMax?为什么是1/2Vdd?

什么叫Vt,白话讲就是看栅极对沟道的控制能力,也就是Id/Vg的求导,其实就是栅极电压的耦合程度。那我总是希望通过电流来体现沟道开启的能力,在饱和区Id/Vg的求导就是0了,所以栅极对沟道已经失去控制能力了,所以我们需要在线性区测试Vt,而线性区的条件是Vd<Vg-Vt,所以Vd=0.1V就可以满足永远Vd<Vg-Vt了。那Gm为啥先升后减呢?由于有亚阈值电流的存在,所以Id-Vg曲线总是平滑过度的,但是选取哪一点作为Vt是个很麻烦的问题,所以业界采用了ASTM F617‑86标准方法:跨导法。在线性区,随着栅极电压的增加反型层厚度增加,导电层增多,所以Drain电流增加,所以跨导Gm增加,这个非常容易理解。可是当Vg继续增加时,反型层厚度增加也导致沟道里面的载流子增多,散射增加,所以抑制了Drain电流的增加速度,但是随着Vg的增加它还是增加的 (同比增加,但是环比是减小的)。在Gm最大的时候也就是载流子速度最大的时候。为啥是Vt=Vgs-1/2*Vdd?因为Idlin=W/L*Cox*μ*(Vgs-Vt-1/2*Vds)*Vds对Vg求偏导的Gm的切线与X轴的交点刚好是Vt+1/2*Vdd。实际上,Gm的最大值刚好发生在线性区与饱和区的交界处。如果对理论很感兴趣,推荐阅读:《Semiconductor Material and Device Characterization》p222~p226。

好了,理论讲完了,我们的回到我们PIE自己的工作上来,到底Vt shift了,我们如何查case啊?

我们就从影响Vt的因素来逐一说明,以及如何排除,原理请参阅Vt公式(http://ic-garden.cn/?p=489)

1)GOX电性厚度TOX: 厚度越厚,Vt绝对值越大,因为耦合作用越难,所以需要更高电压来耦合。所以不管是NMOS还是PMOS的开启电压都是绝对值增大的,如果一个增大一个变小那肯定就是不是它了。同时,如果是Analog制程有测Beta的话,应该也可以有反应的。

2) Vt_IMP: 这个自然没得说了,调节开启电压的。但是通常每个器件都有自己的Vt_IMP,所以没打到的如果也跑了,那自然就不是它了。(有些是一道Vt_IMP同时打NMOS和PMOS,那应该都要shift,而且一定是一个绝对值变大一个绝对值变小,这样才make sense)

3) WELL和APT implant: 这些可以通过Vtf以及VTB排除。它则只会影响一种MOS,要么NMOS要么PMOS,不会同时影响。

4) Plasma Damage(GOX有电荷或者界面态): 这个可以用跨导,当然也可以用我前面讲的C-V去澄清。

5) Poly掺杂:影响功函数,可以看Rs_PO, etc.

6) Thermal budget:热预算越多,导致NMOS/PMOS表面浓度都变低,所以NMOS和PMOS应该同时shift,而且应该是同trend,类似GOX。那我们就只能靠TOX来排除到底是GOX问题还是Thermal的问题了。

上面这些都是同时会影响长沟(20x20um)和短沟(20x0.35um)的,但是实际上我们很多时候只有短沟Vt跑掉了,而长沟没跑。那怎么办?所以要特别看影响Leff的参数,比如Poly CD,Spacer CD,以及LDD/N+ implant了。当然这些参数不见得所有的短沟都很敏感,所以还是要平时多做sensitivity/window去收集你的technology的敏感性。(不要太教条啊~)而且要根据这些process factor影响的其他item来辅助判断,比如Poly CD一定影响continuty poly,spacer还会影响其他poly 肩膀最后导致poly多形成了silicide等等,或者影响Isub等等。

所以查VT shift的case就是多看长沟、短沟,以及NMOS和PMOS这四种组合来判断。再辅助其他参数,比如Rs,Ioff, BV, Isat等来判断。

所以说PIE工程师也是一个系统工程师,不仅要理论,还要有逻辑!

支付宝打赏

支付宝打赏  微信打赏

微信打赏