功率半导体和5G的新宠-《GaN和SiC》:Part-1 (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

最近MtM (超摩尔定律)的热门话题应该是电力电子以及5G了,刚好这两个半导体制造都要用到一个叫做宽禁带的半导体材料,我就来总结一下吧,抛砖引玉供大家入门学习。

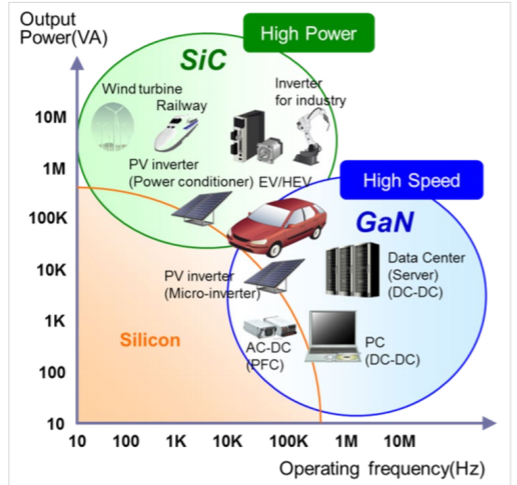

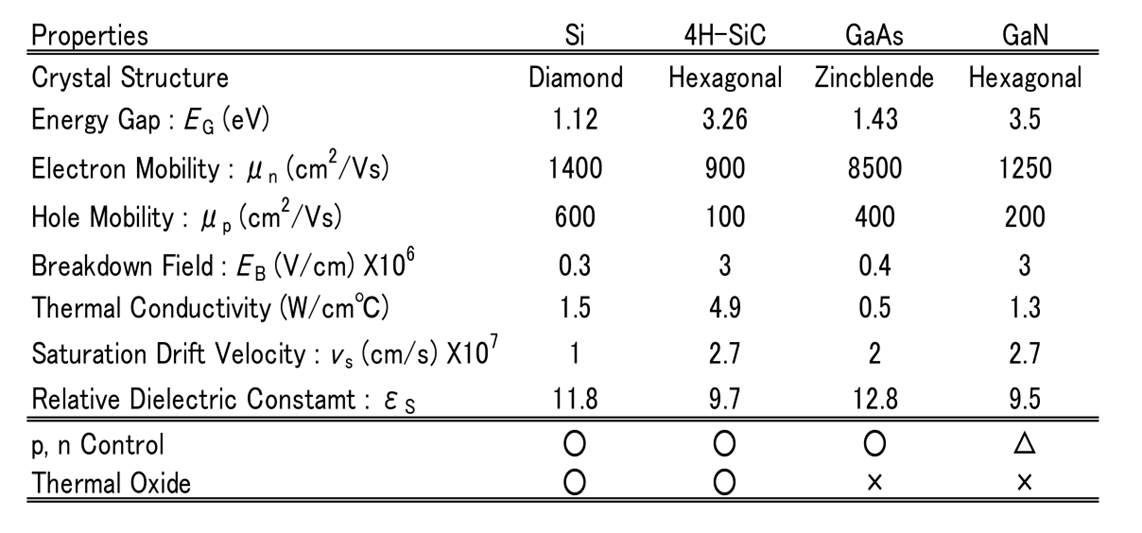

半导体产业的发展一共分三个阶段,第一代半导体材料是硅(Si),第二代半导体材料是以GaAs和SiGe为代表的微波器件,而现在最热门的是第三代半导体材料是宽禁带半导体材料GaN和SiC,相较前两代产品,性能优势显著并受到业内的广泛好评。第三代半导体具有高击穿电场、高饱和电子速度、高热导率、高电子密度、高迁移率等特点,因此也被业内誉为固态光源、电力电子、微波射频器件的“核芯”以及光电子和微电子等产业的“新发动机”。发展较好的宽禁带半导体主要是SiC和GaN,其中SiC的发展更早一些。

功率半导体围绕着硅(Si)发展了半个世纪,一直在BV和Ron之间博弈,也是一个功率器件最基本的门槛。这两个参数一个决定了器件的极限(BV)一个决定了器件的性能(Ron),这就如同鱼和熊掌不可兼得。而在BV的提升上面,主要考虑有源区(Active)和场区(Field),而Active区的击穿电压自然就是靠PN自己了,没其他办法,而场区也是最后器件电场线集中收敛的地方,所以这个区域的电场会很强,所以很容易在这里击穿,所以如何提高终止区的击穿电压成了硅基功率器件的重点,当然发展了这么多年最行之有效也是最成熟的方法就是保护环(Guard Ring)和场板(Field Plate)或者搭配来实现终止区的耗尽区宽度进而降低表面电场,使得击穿尽量发生于Active区的PN结。理论上只要这两道环设计的好,都能使得器件的击穿电压达到理想的PN结击穿电压。但是即便如此,受限与硅材料本身的特性,他的击穿电场也是要受限于他的禁带宽度(Eg)的,所以硅基的功率器件在1000V以上的应用时候就显得非常吃力,而且制造成本和可靠性等等都非常高,急需要寻找一种宽禁带半导体材料来获得更高的击穿临界电场以及电子迁移率,而目前这种材料就是SiC和GaN这两种材料。

话说新材料找到了,但是要全面取代硅基还是很困难啊,毕竟硅基器件的衬底和制造技术已经很成熟,价钱就可以秒杀你。所以在高压高功率的市场,一直存在着硅基功率器件和SiC/GaN的市场争夺战,其中硅基最得意的作品就是Si-IGBT和Super-Junction了。IGBT大家可以参考我之前写的文章,而Super Junction如果大家有兴趣我后面再单独讲解,今天的主题不在这里哈。

好了,言归正传,继续讨论SiC和GaN吧。

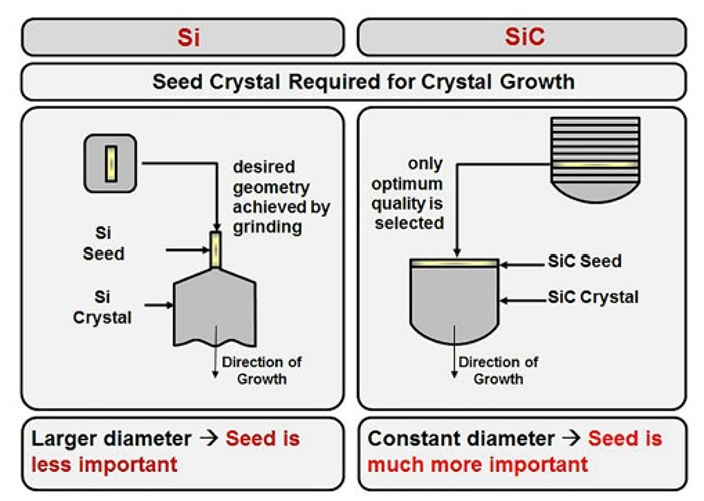

1、衬底片生长(Crystal Growth):这是最基本的,就如同硅基在70年代一样,如果没有单晶衬底片,所有的制造业都是白谈,即使硅基的Si-ingot到目前为止全世界也只有5家可以拉单晶啊,可想而知多难!到了SiC和GaN那就更难了,几乎这就是主要制约这个行业发展的关键因素。

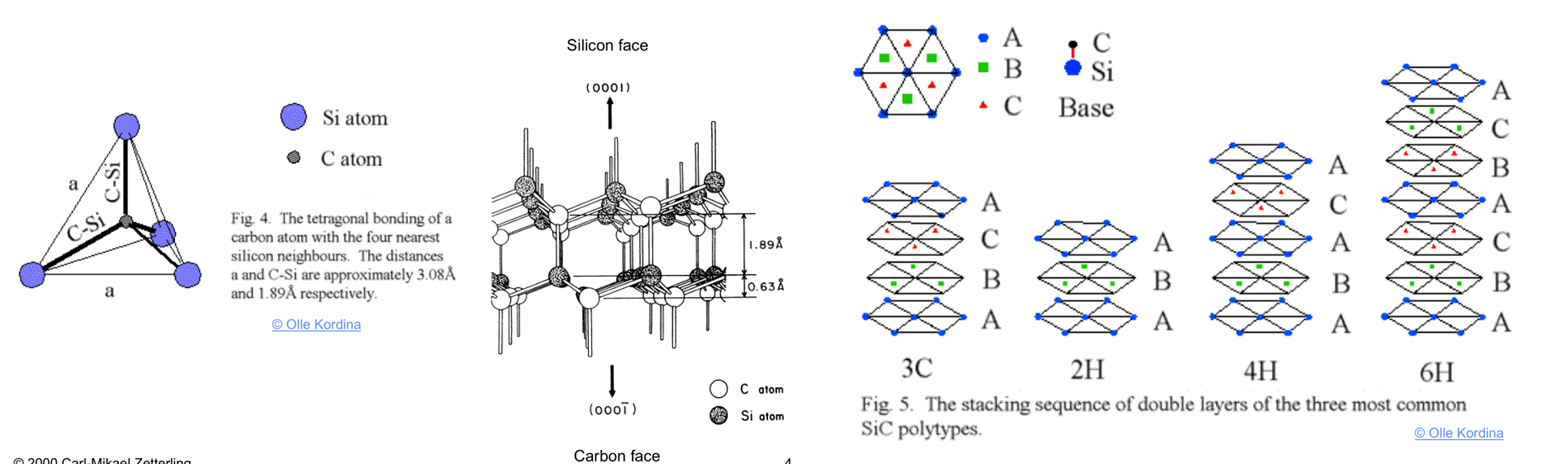

1)SiC制备:先说说SiC的结构吧,大家应该经常看到4H-SiC和6H-SiC,这是指他的堆叠层数。我从头讲起吧!首先,SiC都是第四主族的元素,所以每个Si和每个C刚好一一配对形成稳定的共价键结构,每个Si外面四个C,而每个C外面也是4个Si,也就是如右图的晶体结构。从结构上看,如果你正对Si面看下去的话,背面被挡住了一个C,所以你还能看到三个C,相同的情况,如果你正对着C面看下去,背面也被挡住一个Si,所以你还可以看到3个Si。因为一个C配一个Si,而刚刚说的不管从哪个原子看过去都可以看到三个另外原子,所以最好的晶体排布方式就是六边形结构,也就是书上说的六方最密堆积(HCP: Hexagonal Close Packing),如果不熟悉的话大家一定知道体心立方(BCC)和面心立方(FCC)吧,跟他差不多,也是一种晶体结构而已)。现在开始排布,第一层为A的球代表了双层Si和C的结构,那么下一层根据共价键的价键结构可以有两种分布,分别是B和C。而且A的下面一层只能是B或者C,不能是A自己,B和C也一样。所以这就有了多少种组合?ABA、ACBA、ACABA、ACBACBA,分别对应2H、3C、4H和6H了,而这个数字呢就是代表下一次重复前堆叠的层数而已,而目前SiC的功率半导体都是用4H-SiC或者6H-SiC,主要原因是他可以拉出比较大的wafer而已。

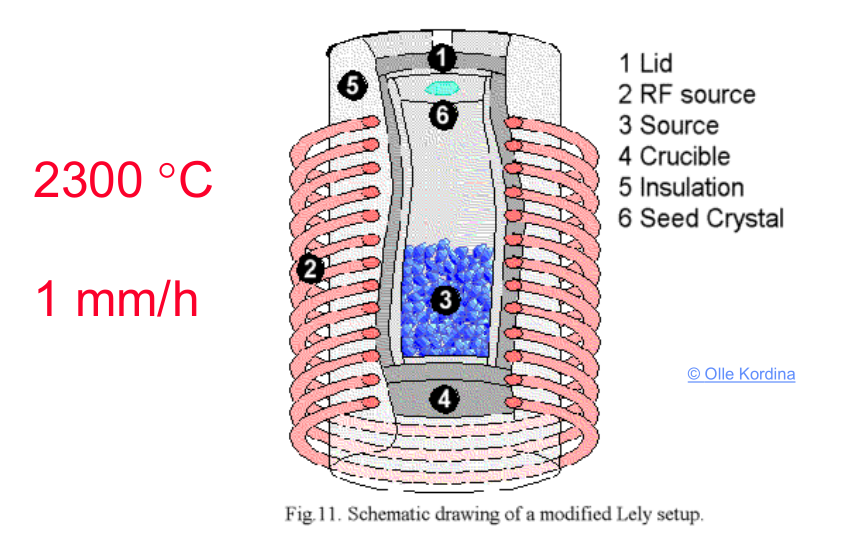

这个结构已经有了,关键怎么制造出来呢?和Silicon一样,CZ直拉的,但是条件非常非常苛刻。第一个是Seed,我们硅Ingot的拉单晶所需的seed很小,wafer的直径和seed大小无关,但是SiC的seed直径直接决定了final wafer的直径,所以seed必须很大。。。

其次是反应条件,温度已经不是Silicon的1400C了,而是2300C,所以加热系统已经是RF coil,且坩埚替换成了石墨(graphite)。他其实是一种物理气相沉积(PVD),只是他不是Sputter的而是加热沸腾然后冷凝到seed表面形成的ingot而已。生长速率只有1mm/hour,急死人了,所以可想而知SiC的价格多贵了吧,据说一两千刀。而且尺寸目前只能做6寸,主要是受wafer表面的温度均匀性限制,而且doping level没办法做高,如果要想用high doping的SiC衬底,必须要用CVD EPI的方式来重新生长(1400C~1600C, 3um/hour, SiH4+H2+CH4+C3H8, etc),而且doping的元素主要是Al和Boron为P型,而Nitrogen和Phos为N型。如果是离子注入(Ion Implant)的方式来doping的话,会引入晶格损伤,而这种损伤很难消除,必须要用高温离子注入(High Temperature Implanter: 700C)以及高温退火(1200C~1700C)才能缓解和消除,这就是process里面最大的挑战!

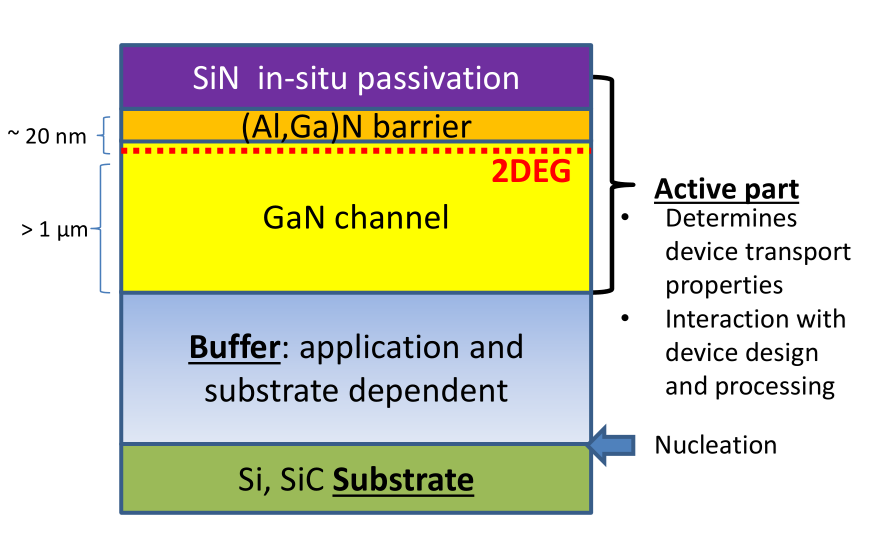

2) GaN衬底:GaN主要都是MOCVD或者分子束外延(MBE)在衬底上长一层GaN而已,但是对于衬底的选择很重要,如果是作为功率的switch器件,都是选择GaN-on-Si,如果是用作RF的话,就需要选择GaN-on-SiC,显然后者受衬底依耐比较大,仅限于6寸晶片。至于他是怎么外延的,为什么要有成核(neuclization)和buffer层等等,必须要先懂他的器件原理才能理解,后面讲器件的时候一起讲吧。

Si上的GaN已经证明了现有GaAs技术的原始功率密度仅为8倍,同时将效率提高到70%。GaN on Si性能现已与SiC衬底上更昂贵的GaN相匹配。而且在Si上使用GaN允许供应商转移到8寸晶圆厂达到cost down。在这里,CMOS工艺控制通常可以使线路产量高于98%。由于CMOS正在解决的终端市场数量极高,平衡产量和成本动态至关重要,如果能推到8寸,其cost可以降低10倍,而且产能足够。

2、器件工作原理:留着另起一个专题吧,太复杂了!这里只是买个伏笔吧。

1) SiC器件: SiC器件方面,主要跟Silicon结构差不多,也需要氧化和PN结等,还是Diode (FRD, SBD, etc), MOSFET, IGBT,等等。国际上SiC肖特基二极管(SBD)、金属氧化物半导体场效应晶体管(MOSFET)等均已实现量产,产品耐压范围600V-1700V,单芯片电流超过50A,并开发出了1200V/300A、1700V/225A的全SiC功率模块产品;实验室开发了10000V-15000V / 10A-20A的SiC MOSFET;并研发出了IGBT芯片样品,最高耐压水平已经超过20 kV量级。

2)GaN器件:主要是靠异质结的极化产生压电效应(piezoelectric polarisation),最后在异质结交接处产生两维电子气 (2DEG: 2-D electron gas),而这个电子气的速度比普通的电子快2.7倍,所以速度很快,但同时他也是常开状态(耗尽型器件)。还有一些场板设计等等后面再说。所以这种器件的key在于异质结是否做的好?稍微有个晶格缺陷就挂了,搞来搞去还是衬底材料是重点啊!所以GaN的器件又叫HEMT: High Electron Mibility Transistro)

我们期待技术的成熟,当价格能降到硅器件的2~3倍,市场肯定会被SiC和GaN全面取代掉。尤其是2020年以后,全球普及EV汽车的时候,根据预测,直到2020年我们几乎有21%的年复合增长率。

支付宝打赏

支付宝打赏  微信打赏

微信打赏