CMOS器件历史浅析–扫盲版 (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

编者注:这个只适用于没有基础的common course,如果大家了解的话直接跳过,不过可以简单看看发展史吧。

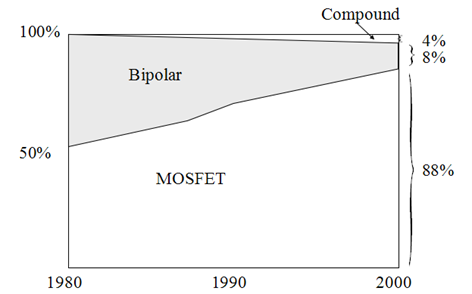

上一章节我们讲过BJT Device,如果大家还记得的话,它应该电流工作型器件,而且是双载流子(Hole/Electron)同时工作的。所以它通常用于电流或功率放大型,或者用于高速器件(ECL: Emmitter coupled Logic)。上个世纪60年代之前都是BJT的天下,也是人类史上最早的IC chips,在1961年的时候,一个BJT器件得要40 dollar,不得了哇,直到1970年代才开始逐渐被NMOS, CMOS取代逻辑运算领域,但是在模拟(Analogy)以及功率型(Power)应用领域任然无法取代,所以现在市场上依然有BJT器件的存在。

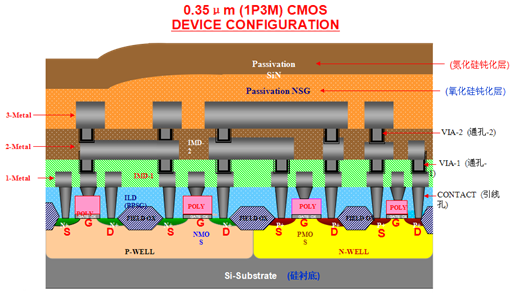

要说CMOS,咱半导体人第一个知道的一定是NMOS,因为大家培训都是用NMOS,O(∩_∩)O哈哈~。但是你知道吗?世界上第一个MOS却是PMOS,发明于1960年,用于简单的数字逻辑器件(digital logic),但是速度太慢一直没有市场。直到1970年世界上第一颗NMOS出现且速度比PMOS快了2~3倍(因为电子的迁移率/mobility是空穴的2.5倍),并很快取代了PMOS之后,MOS晶体管才逐渐有了市场。但早期主要应用于手表和计算器。直到1980年,人类发明了Well(阱),注解: 因为NMOS要在P-Si里面,而PMOS要在N-Si里面,所以一个单一掺杂的硅片(wafer)上无法同时做NMOS和PMOS。才有了CMOS (Complementary MOS: NMOS+PMOS),此后开始进入摩尔时代 (摩尔定律/moore's law发表于1975年IEEE)。

MOS的结构如下图,“Well(阱)”/或者Substrate用来装这个MOS的,NMOS必须是P-Well或者P-Substrate,除了well还有“源极(Source)” 和“漏极(drain)”,源极顾名思义类似三极管的发射极,他是载流子(carrier)的源头,那漏极就类似三极管的集电极,用来吸收源极过来的载流子了。还有一个就是“栅极(Gate)”,在台湾的教材叫做闸极。顾名思义Gate就是门或者闸门(知道为啥逻辑电路很多叫做门电路了吧~?)。所以MOS是个四端器件。

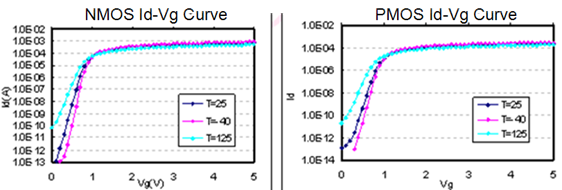

从MOS四个端子的命名就知道了,当初人们就是把它等效为一个水龙头或者连通器,Gate就是开关,只要打开开关水流从源端到漏端逐渐增大,当开关开到最大水流自然也就饱和了,所以MOS的电流电压特性曲线(Id-Vg)如下图。那么在半导体器件里面,理论上他是怎么开启的呢?从结构上我们知道,NMOS的衬底是P-Si,而Source和Drain都是N-Si,所以中间的沟道和两边的Source/Drain形成了两个PN节让Source/Drain彼此隔离,而中间的沟道上面与Gate之间有一层薄薄的Oxide (gate oxide,栅氧),当栅极加正电压(Vg),由于Gate oxide (GOX)不导电,所以这个电压只能停留在gate上靠电场感应使得P-Si里面的少数载流子在电场作用下吸附到表面逐渐耗尽(depletion)表面的P-type,当沟道表面的少数载流子电子积累到一定程度后就会逐渐反型(Reversion)成N-Si,使得Source和Drain连起来,达到开启沟道的目的。PMOS原理类似把所有的掺杂type和电压反过来就行。

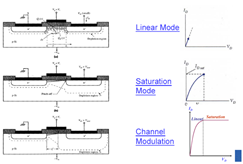

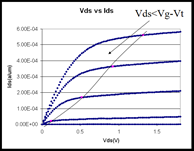

喜欢思考的人一定会问另外一个问题,连通器的水流大小除了由连通器的开关决定外,应该还有一个因素就是连通器两端水压的高度。那MOS管电流除了Gate电压Vg外,应该还有一个Drain端电压?You're definitely right。当Gate开启后,如果Drain没有电压,则没有压差所以不会产生从源到漏的电子流(电流方向从漏到源),随着drain电压升高,电流自然逐渐升高,此时是成线性增长的,我们称这个期间工作在线性区(liner region, Idlin=μ*Cox*W/L*[(Vg-Vt)*Vds-1/2Vd^2])。当Drain电压继续升高,连通器的管路只有那么粗,所以水压再高也过不来了,此时就到了饱和区(satuation region, Idsat=1/2*μ*Cox*W/L*(Vg-Vt)^2)。当然在半导体理论里,饱和区的原因是因为载流子在电场加速下的速度饱和(因为载流子加速会碰撞,自然就抑制电流增大)。所以就有了另外一组Id-Vd Curve。

上面右图的Id-Vd curve中,Id在饱和区时不是绝对的不变,而是略微上翘,原因是一个名词叫做沟道长度调制效应(Channel Length Modulation)。从上面的Isat公式可以看出Isat与W/L称正比,所以L变小自然电流变大。因为gate开启时,Drain电压逐渐增大,Source接地,所以靠近Drain端会产生一个夹断点(pinch-off),此时到达饱和。如果Drain电压继续升高,pinch-off向source端扩展,所以Leff(有效沟道长度)减小,所以Isat会略微升高。

学术上,线性区的条件是Vd<Vg-Vt, 反之饱和区的条件就是Vd>=Vg-Vt。

讲完了结构,再来讲什么叫MOS?MOS也叫MOSFET,全名叫做Metal-Oxide-Semiconductor Field-Effect-Transistor,他的Gate是由金属和氧化层(GOX)组成,你们现在看到的Gate的电极是Poly,但是1970年代的Gate是Al,所以叫做Metal-Oxide,那个年代是先做Source/Drain,再做Gate,所以Gate和Metal1一起做的。但是这样的主要问题是Gate和Source/Drain的Overlay太大了,所以后来先做Gate再做Source/Drain,这样的问题是Source/Drain要高温激活掺杂,而Gate的Al就无法承受了,所以发展到各位现在看到的Poly gate。但是poly毕竟是半导体,在栅极电压下,掺杂原子会发生再分布,所以靠近GOX的掺杂原子会被拉到上面,这就是传说中的多晶耗尽(poly depletion),而这个耗尽的poly因为不导电就充当了GOX的dielectric。在45nm以下机会又无法使用poly gate了,所以又回到了老祖宗的Metal Gate。所以经常看到28nm HKMG (Hi-K Metal gate,顺便讲下Hi-K,因为GOX对Vt的值很重要很重要,学术上叫做跨导/Gm,GOX越薄,跨导特性越好,Vt越低,可是薄了容易漏电,所以必须要有高介电常数的GOX, High-K)。

最后再啰嗦一下CMOS和BJT的区别吧,BJT是两种载流子同时工作的器件,而MOS是单一载流子。BJT是PN节的节型晶体管,而MOS是场效应晶体管。BJT的线性和噪声特性不如MOS。

我们这里讲的主要都是增强型(默认为关闭),还有耗尽型(默认为开启)。很少用我就不讲了,先睡觉了~~~

支付宝打赏

支付宝打赏  微信打赏

微信打赏