经典:CMOS寄生特性之SnapBack/Latchup (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

Snap-Back和Latch-up应该是CMOS寄生特性里面最经典的理论了,其实他两个是同一个东西,都是NMOS和PMOS的寄生三极管等效电路开启进入正反馈状态下的回路导通状态,叫做Snap-back是因为当寄生回路触发导通之后,会迅速进入低阻状态,所以I-V曲线迂回呈现负阻状态,所以叫做Snap-back(侧重工作区域)。所谓Latch-up就是当这个寄生旁路触发导通之后,基本上NMOS和PMOS就被这个寄生旁路短路了,栅极几乎就没有作用了,类似被锁住了,所以中文叫做栅锁效应或者栓锁效应,或者闩锁效应(Latch-up, LU)。所以,当电路外界有一个大的浪涌电压/电流,就会触发栅锁效应,只要电路的电流没有大到烧毁,瞬间断开电源,重新启动还是有救的,所以想想为啥有的时候电脑莫名其妙死机,重启又OK,大部分就是这个原因。(当然很多设计就是要屏蔽外界的输入不稳的问题)

这个理论虽然是寄生特性的分析,但是后面很多器件和设计都会用到,最经典的就是ESD保护电路,还有将来要讲的IGBT器件,都要靠这个理论才能懂。所以我们要在这一章把这个理论学透(其实还是三极管理论,前面讲过的哦~~)。

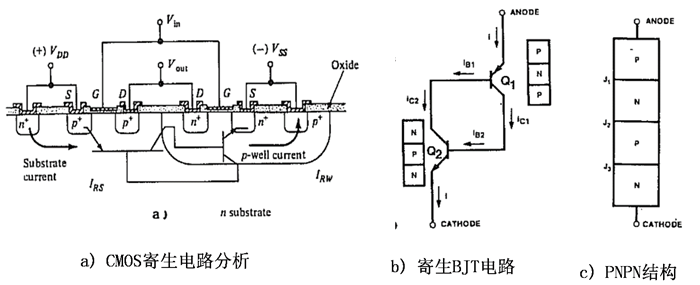

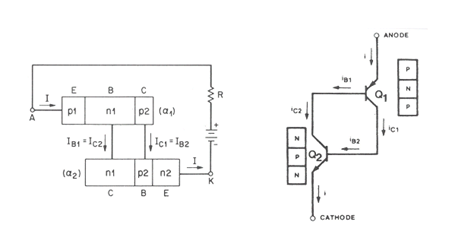

我们先看看CMOS里面,一个NMOS和一个PMOS。如下图,NMOS的源漏(N+)与PWELL以及PMOS的NWELL组成一个NPN三极管。同理,PMOS的源漏(P+)与它的NWELL以及NMOS的PWELL也组成了一个PNP的三极管(图a)。所以他们各自的Well既作为自己BJT的基区,又作为另一个BJT的集电区(一个Vertical,一个Lateral),所以串联起来就是一个PNPN的结构(图c)。(这里一定要理解透)

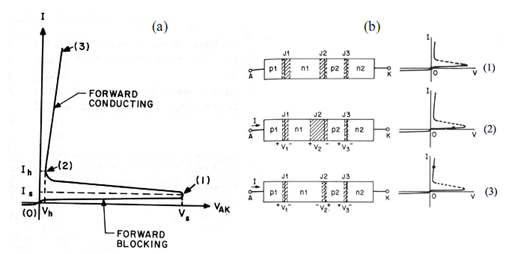

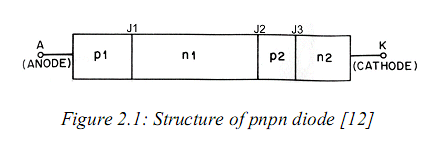

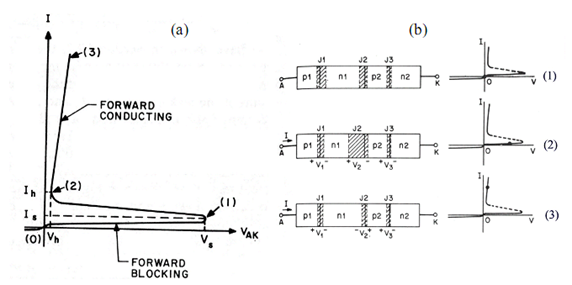

再来研究这个PNPN的结构,它是一个双稳态的结构(Bi-Stable state),因为他是一个可恢复的二极管特性,这样就既可以是雪崩击穿下的导通状态,也可以是不导通下的截止状态。如下图,当A为阳极(Anode),K为阴极(Cathode),当外界电压为正偏(A接正电压,K接负电压),此时,我们的PN结J1和J3是正偏,所以AK的电压几乎都反偏的加在了J2上 (这个可以理解吧~),其实就是把它当成中间一个二极管的反偏特性来分析即可。此时量测它的I-V曲线可以得到三个区域特性(OFF, OFF->ON, ON)。

区域1 (OFF):当阳极A和阴极K的电压很低时,因为J2反偏截止,所以几乎很少电流从阳极留到阴极,所以PNPN的器件处于截止关断状态,也叫正向阻断(Forward-Blocking),或者叫做高阻抗状态(High-Impedance)。这个状态下的电流随着电压增大微微上升。

区域2(OFF->ON):当阳极A和阴极K的电压进一步增加,直至PN结J2达到反向击穿电压(Breakdown),则正向导通(Forward Breakover)会瞬间发生,所以此时叫做瞬态(Transient State),器件从OFF切换到ON状态,使得I-V曲线呈现负阻状态,所以叫做Snap-back。而此时的电压为切换电压(Switch Voltage)为Vs。

区域3(ON):当器件的PN结J2导通了之后,它就单纯是一个正向导通的二极管了,所以它的I-V曲线又变成了一个二极管的正向导通曲线,此时状态叫做正向导通状态(ON),也叫正向导通(Forward Conducting)或者低阻抗状态(Low Impedance)。

所以在上述三种区域里,当工作在区域3时,器件就是ON状态,降低电压低于Switch Voltage时,可以使他进入区域1,器件就是OFF状态了,反之亦然(Vice Versa)。如果外部电路持续供给电流大于Ih,只要电路一直开启则PNPN电路就一直被锁定在ON的状态,这就是我们将的栓锁效应(Latch-up)。

下面我们继续从寄生三极管的电性来探讨栓锁效应(Latch-up)发生的条件,有助于我们理解如何降低栅锁效应,或者如何实时触发栅锁效应来达到ESD保护的作用。

刚开始我们就讲过了,PNPN结构就是两个寄生的BJT连在一起(如下图),一个的基区是另外一个的集电区,所以Ib1=Ic2,Ib2=Ic1 (这个一定要理解透哦)。当这个电流乘以基区电阻能够使得EB结正向偏置(forward biased),使得BC结反向偏置(Reverse Biased),则这个BJT工作在主动放大区,所以Ic=α*Ie+Ico,其中α为共基极电流传输系数。所以对于NPN和PNP两个三极管而言分别的Ic1=α1*Ie1+Ico1 (1),Ic2=α2*Ie2+Ico2 (2),又由于基尔荷夫定律(Kirchhoff's law),I=Ic1+Ic2 (3)。所以将前两个带入第三个公式,即可得到I=(Ico1+Ico2)/[1-(α1+α2)]。所以当α1+α2接近1的时候,则总电流会接近无穷大,也就是ON的状态(break over)。

而在三极管中,α值是随着Ic增大而增大的(因为Ie不变),而Ic来自于CB结的雪崩击穿(Avalanch Breakdown),所以提高Vc是可以提高α的。当α1+α2=1,则总电流I为无穷大,PNPN进入区域3(ON)状态。而此时两个BJT三极管的EB结合CB结都工作在了正偏,所以此时两个BJT都进入了饱和区(SATUATION)。

所以理想情况下,发生Latch-up效应的充分必要条件是α1+α2=1,如果我们换算成β(共发射机电流放大系数),根据β=α/(1-α),得出必要条件为β1*β2=1。当然实际情况是我们还要考虑Well和Sub的阻值,所以我们实际情况发生栅锁效应的条件是β1*β2>>1。

从Snap-back曲线中可以看到有两个拐点(Knee-point),一个是switch-point (Vs, Is),一个是Hold-point (Vh, Ih)。这两个点上的dI/dV=0(也就是切线与X轴平行)。这两个点也是用来评估Latch-up特性的主要考量。

栅锁效应的触发机制(很重要哦):

1. 两个EB结必须都要正偏,这样才能有足够的电流让第二个PN结J2也正偏,从而进入ON状态。

2. 理想情况下β1*β2=1,实际情况下β1*β2>>1。

3. 电路工作电压必须大于Holding voltage (Vh),而浪涌电压(voltage surge)必须大于等于Switch电压(Vs)。才能turn-on PNPN结构进入正反馈。

4. 必须有足够的触发时间,才能从turn-on进入负阻到第二个拐点Holding point,此时才能够保持Latch-up。

栅锁效应的触发模式:

1. 电压增加(Input/output),或者NW/PW雪崩击穿,这两个应该都比较容易理解,我就不说了。

2. Nwell到外部PW里的N+-S/D的穿通(punchthrough):这个要靠design rule来解决了。

3. P-SUB与内部P+-S/D的穿通(punch-through):其实就是导致P+-S/D到NW边缘的距离短了,所以β会增大。也是需要design rule来解决。

4. 寄生的Field transistor: 其实类似穿通吧。

5. 光电子或者辐射射线(Photocurrent/irradiation):让两个EB结正向导通,所以自然就都进入放大区而触发栅锁效应了。

6. 源漏junction的雪崩击穿,或者Isub电流,这些都可以让EB结正向偏置,触发栅锁效应。

栅锁效应的防范措施:

一般有两种机理,一种叫做Latchup-Free(无latchup),一种叫做Latchup-immune(免疫性)。这两种区别大了去了,前者表示我要让他在任何情况下永远都不会发生,而后者是指在Normal下不发生,但是如果有大电流浪(surge)涌或者注入(injection),则还是会发生。学理上我们不可能free吧,所以都是在朝着后者去做免疫性提升,所以尽可能让Holding voltage (Vh)小于Vcc,方法如下:

1. 深阱或者倒置阱(Deep well or retrograde well):减少current gain。

2. 减少电阻:减小well(基区)电压,防止EB结开启。

3. 减少Isub:同上。

4. Layout: 防止穿通/punch。

5. 设计: 放置current sink来减弱/拆分PNPN结,或者是在N-channel器件周围加P+ guard-ring,或者把场区增加使得NMOS和PMOS隔离远点(使得基区长度加大,所以beta就减小了)。

等等等等,都是围绕PNPN结构或者电流放大系数,或者EB结正向偏置。

栅锁效应是product qualification的必做项目,因为是电路里面的(NMOS+PMOS合成),所以它必须在circuit才可以做,而在Device level没法做的哦。

希望此篇是Latch-up/Snap-back的终结篇了。

支付宝打赏

支付宝打赏  微信打赏

微信打赏