MOS器件的深度解析 (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

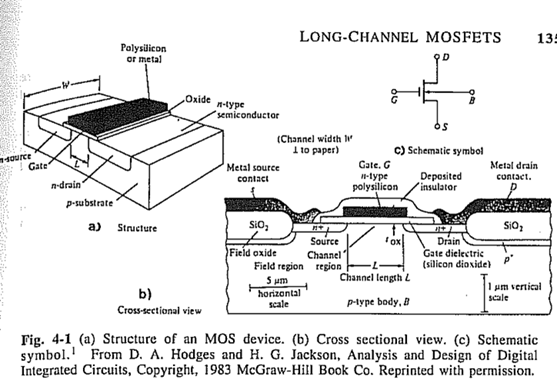

前面几节几乎从结构上介绍了MOS的原理和特性,但是随着尺寸越来越小,电压越来越,很多我们可以忽略的寄生特性(Parisitic)以及我们称之为二级效应的关注点开始变得不可忽略,今天我们就来聊一聊吧。

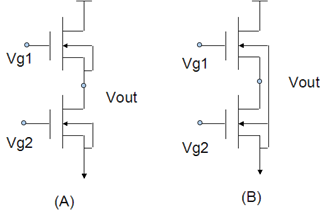

1. 衬偏效应(Body Effect):我们在看MOSFET都是把source和Bulk短接在一起,所以我们忽略了Bulk的电压变化会对器件产生什么影响?当Vbs又原来的0偏电压改为接负电压,这样衬底到源极的PN结反偏耗尽区会变宽,所以衬底的耗尽区会变厚,所以耗尽层中的空间电荷会变多,所以栅极(gate)需要更高的电压来让它达到完全开启。所以开启电压会升高(感谢xp的提醒指正,不然不知要误导多少人)。这个在器件上你觉得无所谓,但是对设计的人就怕了。请看下图,当两个NMOS串联,在中间输出点的电压应该等于1/2*Vdd,所以上面的NMOS和下面的NMOS如果分开各自和source短接,那么这两个NMOS的Vth肯定就不match了,除非你像右边那样都接ground。

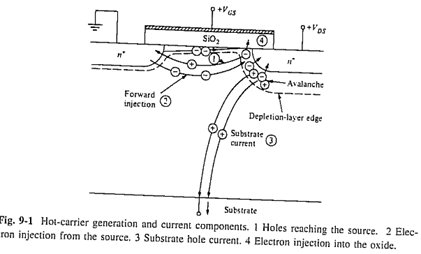

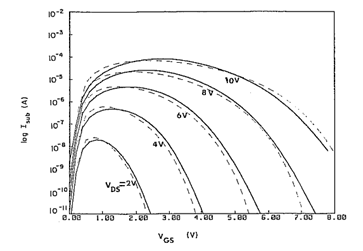

2. 衬底电流(Isub):上一张讲了下热载流子特性(HCI, Hot Carrier Injection),主要由于有效沟长(Leff, effective channel length)变小之后,沟道电场变大导致电子加速碰撞晶格产生更多的电子-空穴对(Electron-Hole pairs),而新产生的电子空穴对里面的电子一部分被Drain吸收使得Ids增大,另一部分被Gate垂直电场吸收撞击Si-SiO2 interface产生界面陷阱电荷(Qit)。另一方面,电子空穴对里面的空穴会就被gate垂直电场加速推到底部进入衬底/well成为Isub。

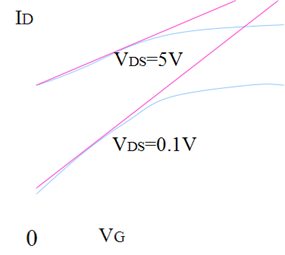

所以,随着Gate电压Vg的增加,刚开始沟道载流子增多,撞击也会增多,所以Isub会增大。但是继续增加Vg电压,载流子继续增多沟道里面的载流子无序撞击增多(人多了总会碰碰撞撞),所以迁移率减小,而且随着Vg逐渐靠近Vd的时候,Drain端的横向电场会被Gate的横向电场减弱(DIBL, Drain Induced Barrier Low),所以Isub又开始减小。

3. 亚阈值特性(Subthreshold):有些叫做Subthreshold slop (St) 或者叫 Swing。我们知道当Vg电压升高时,Channel表面先开始耗尽(depletion), 弱反型(weak inversion),强反型(strong inversion)并完全开启。所以在沟道没有完全开启之前随着电压升高,已经开始有漏电,理想情况是过渡区电流越陡峭越好。所以swing是看在weak inversion时候Id随着Vg变化而变化的程度 (ΔId vs. ΔVg)。swing越大亚阈值漏电越大。

推荐一篇文章:

3-1 MOS场效应管(北邮)

http://wenku.baidu.com/view/0b55f13ca8956bec0875e32e.html

还有DIBL和GIDL留给明天吧,今天休息了~~

支付宝打赏

支付宝打赏  微信打赏

微信打赏