MOS器件理论之–DIBL, GIDL (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

前面几乎讲了MOS的结构原理,热载流子(HCI),穿通(Punch Trough),亚阈值(Swing/St),长沟、短沟、宽沟、窄沟等特性。几乎基本的都讲完了,还剩下一点就是DIBL和GIDL了(以前在学校,我总分不清这两个关系),后面再说Burried Channel和Poly Gate Depletion吧,貌似还有Source-Well-Drain寄生的三极管相关的特性(Snap-Back和Latch-up),我会再陆续讲完。

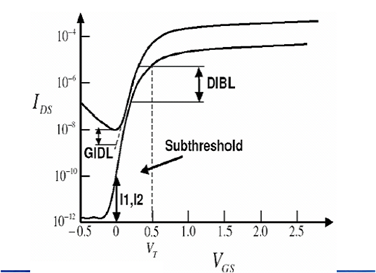

1) DIBL (Drain Induced Barrier Low):也叫漏极感应势垒降低,其实这就是短沟道效应的理论解释,以前总是讲沟道长度缩小,Vt也会减小(RSCE除外),但是在Vt的公式里又找不到与沟道长度相关的参数,所以很难理解。下面就来仔细理解一下。

MOSFET的阈值电压(Vt)的影响factor主要有三部分组成,首先是抵消功函数(Work Function)以及GOX电荷所需电压,也就是平带电压(Vfb),我们PIE对Vt的了解就这些了,但这只是最基本的。Vt的第二部分为产生强反型时所需的表面势(2φ),第三部分为强反型时Gate下的由栅极控制的表面电荷(Qb)在氧化层上产生的附加电压,所以阈值电压公式为: Vt=Vfb+2φ-Qb/Cox (1)。

其中Qb=-γ*Cox*sqr(2φ-Vbs),所以Vt=Vfb+2φ+γ*sqr(2φ-Vbs)。其中γ为衬底偏置系数sqr[(2εs*q*Na)/Cox]。

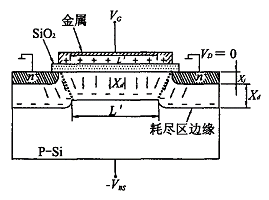

公式(1)中,Qb是指强反型时Gate下的由栅极控制的表面电荷(Qb),如果没有源和漏的情况,下面的沟道的反型电荷应该是矩形,但是由于源极和漏极对沟道区的耗尽效应抵消掉沟道下面栅极控制的电荷(电荷共享/Charge Sharing),所以成为倒梯形(如下图),所以实际的Qb(梯形面积)会比理想情况小。所以沟道长度越短或者Drain端电压越高,都会导致这个耗尽区往沟道里面延伸,所以Qb会进一步减小,所以Vt减小。

如何减小这种DIBL效应?所以必须要增强栅极对沟道电荷的控制能力,所以必须降低GOX厚度。

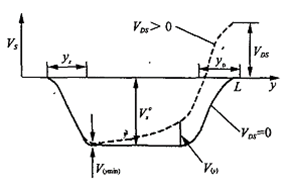

接下来我们来解释一下为什么沟道长度减小,会使得漏电流增加?现象上我们知道是因为穿通(punch through),但是从机理上看又是为何?当我们减小沟道长度,增加漏端电压,漏源耗尽区越来越近(穿通),会使得电场线从漏到源的穿越,使得从源端注入到沟道的电子增加,导致漏电流增加。其实这个就是个两维的电场分布问题,横向有漏端电场,纵向有栅极电场,然后解二维泊松方程就知道了,当然我不会,呵呵。

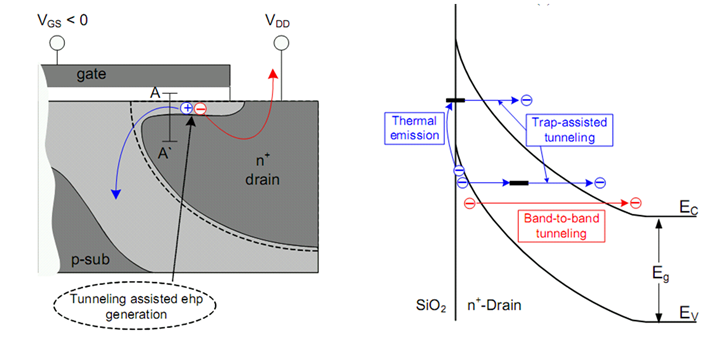

2) GIDL (Gate-Induced-Drain-Leakage):栅感应漏极漏电流。我们通常讲MOSFET漏电流(Ioff),都知道是漏源之间亚阈值漏电流,或者Drain到Well的PN结漏电流,或者栅极漏电流等等,但是我们还有一个叫做栅感应漏极漏电流,发生在栅漏交叠区的下面。因为从器件结构上Gate与源漏必须对齐,但实际不可能绝对对齐,肯定有交叠,而Drain与Gate交叠的区域下面(以NMOS为例),当Gate电压小于0时,并且Drain加工作电压时,它会在交叠区下面的Drain上积累耗尽/深耗尽原来的N-Si,而导致Drain的强电场加在了这个耗尽区里面产生辅助陷阱的载流子复合(Trap-Assisted Carrier-Generation),其过程为先从价带到陷阱,再从陷阱到导带的过程(如果电场够强,则不需要陷阱也可以直接隧穿过去)。也就是传说中经典的Band-To-Band-Tunneling (BTBT)。

在半导体芯片中,GIDL因为是Vg<0时的漏电,所以它主要贡献关态(off-state)漏电也就是待机漏电流或者是热损耗(Heat Dissipation)。所以现在讲究待机的移动终端这个必须要严格控制,典型为<10pA/um。从工艺角度上,主要造成GIDL的因素有哪些?当然最主要的就是Drain与Gate的Overlay,所以要想方设法把Drain和Gate拉开(但不能脱离),比如增加poly oxidation,或者增加Spacer宽度,减少LDD dose,等等。另外还有一些导致GIDL的因素,比如S/D的pre-amorphos implant,或者HCI导致的interface损伤,或者GOX的F-N tunneling等等都会导致GIDL漏电增加。

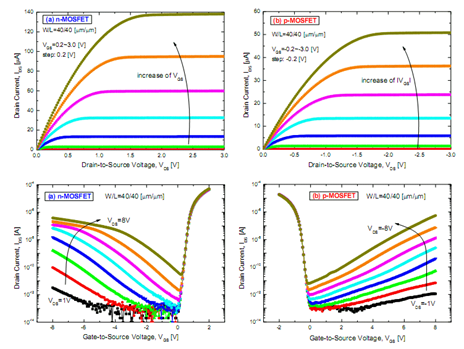

从Device I-V curve的角度,我们一般收Id-Vg curve多scan Vg<0的那一段就可以评估它的GIDL特性了。

支付宝打赏

支付宝打赏  微信打赏

微信打赏