解剖CMOS门电路–《与非门》 (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

CMOS是半导体制造或者器件的最basic,所以我选择专题讲解CMOS与非门,从CMOS与非门的工作原理到电路分析到芯片解剖,刚好这是我大学的毕业设计现成的材料。这次写的最轻松了,不过也是原创哦,虽然是十年前的,哈哈~~。虽然十年了,依然对老唐心存感激,当年差点随大流报名BBS网站开发了,还好自己去解放碑赛格买了个电路回来死乞白赖的找唐老师,还好后来恩准了。

1、CMOS与非门原理:

任何复杂的逻辑功能均可分解为“与”、“或”和“非”操作。通常,CMOS采用正逻辑。对于P管是“串或并与”,而对N管则为“串与并或”。以此可以构成CMOS或非门和与非门。

目前CMOS静态门电路在超大规模集成电路芯片中是非常重要的功能电路。例如在门阵列器件中几乎完全采用CMOS静态门。又如在微处理器及其外围电路中,大部分的控制接口逻辑电路是用CMOS静态门实现的。CMOS静态逻辑电路所以能取得这样的地位主要是由于该电路简单、可靠。

CMOS静态门电路用增强型NFET做下拉管,而用增强型PFET做上拉管,同其他结构的逻辑电路相比CMOS静态门可实现更为对称的上拉和下拉操作。而且在逻辑门处于静态下没有直流通过,其结果是:(1)逻辑电平等于电源电压值(Vdd和地),故逻辑摆幅最大,(2)CMOS静态门为无比(Ratioless)电路,即门电路的正确操作与PFET和NFET的相对尺寸(两管沟道宽/长比的比值)无关。

静态CMOS逻辑门是由完全对称的NMOS和PMOS晶体管阵列构成的,图2-1给出一个含有任意门的方框示意图。每个输入A,B,C,…同时都连接到一NMOSFET(Ā方框内)和一PMOSFET(A方框内)。

当某条件满足Ā=o和A=1时,它表明上部的A方框内的PMOS FET导通,而此时的Ā方框内的NMOS FET截止处于开路。在此情况下,输出节点与电源电压Vdd接通,故输出为高电平。反之,当条件为Ā=1和A=o时,下部Ā方框内的NMOS FET导通,上部A方框内的PMOS FET截止处于开路,输出节点与地接通,将输出电平下拉至地。

逻辑门电路的设计基本围绕着三个主要任务:形成所需逻辑功能,建立电路的直流特性和分析电路的瞬态响应。逻辑功能的建立是通过上图中Ā和A方框内的串联和并联连接的MOS FET的恰当的布局来实现的。而电路的电特性(直流特性和瞬态响应)则取决于器件的沟道宽/长比、逻辑晶体管的连接和几何版图。

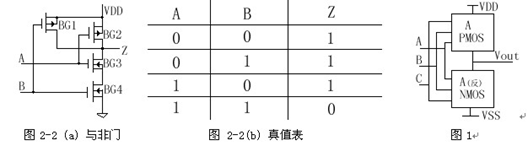

CMOS二输入与非门的电路、真值表分别示于图2-2的(a)、(b)。其中BG1和BG2是增强型PMOS管,它们的源极并联接到正电源Vdd,漏极并联与BG3漏极连接。BG3和BG4是增强型NMOS管。每个PMOS管的栅极与一个NMOS管的栅极连在一起,作为信号输入端。这种PMOS管并联而NMOS串联的结构是CMOS与非门电路的特点。

CMOS电路结构有一个特点,即当电路输入高电平时,PMOS管截止,而NMOS管导通;当电路输入低电平时,PMOS管导通,而NMOS管截止。这是学习CMOS电路的基本原则。根据这个原则,可知CMOS与非门的工作原理是:当输入端A、B中有一个或两个同时是低电平,则NMOS管BG3与BG4中至少有一个是截止的,PMOS管BG1和BG2中至少有一个是导通的,所以输出Z为高电平。只有当两个输入端全为高电平时,两个串联的NMOS管BG3和BG4才同时导通,而两个PMOS管BG1和BG2同时截止,使输出Z为低电平。由此可见,电路的输出Z与输入A、B之间是与非关系。

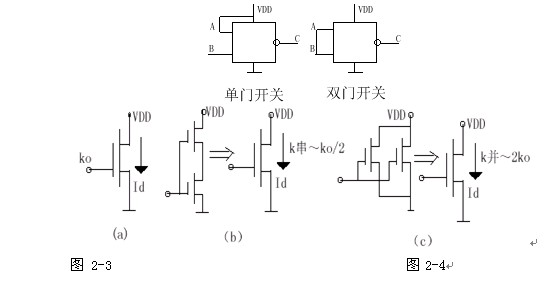

在门电路的工作中,与反向器有着共同之处,仍以二输入的与非门为例,当A或B其中任何一个输入端为低电平时,因为T1或T2管有一只导通,并且T3或T4管有一只截止,故输出都为高电平。只有当A和B同时为高电平时,了T1和T2管都截止,T3和T4管都通导,输出为低电平,完成与非逻辑功能。我们把它用图2-3中所示的两种方法,测量其传输特性。上左图是仅在一个输入端(B)输入信号,另一输入端A接电源,称为“单门开关”。上右图是把两个输入端并联在一起输入信号,称为“双门开关”。则它们的传输特性如下图所示。在高增益区的特性曲线分为两支。分别对应两个转换电平V单*和V双*。这是因为多输入端门中负载管和输入管的并联、串联效应所引起的。为了说明这一现象,我们先讨论一下MOS晶体管的并联和串联时的情况。

考虑一个MOS晶体管(N沟道)。其电流常数为k0,如图2-4(a)。如果把两只特性相同的MOS管分别串联和并联起来,则串联的管子总夸导下降,并联的管子的总夸导增加。如果用一个新的等效MOS管来代替,则这支等效的阈值电压不变,而其k串U1/n*k0,k并=n*k0。这一结论可以用来讨论和分析与非门的性质。

我们再来看图2-4(a)中的电路。在双门开关时,输入端为低电平,T1和T2管全部导通,T3和T4管全部截止。当输入电平逐渐增加经过转换区时,T3和T4管也导通了,这时电流流过两只并联的T1和T2管和两只串联的T3和T4管,见图2-4(b)。若把他等效为一个倒相器,则等效倒相器的负载管电流常数为kp等=2kp,输入管的kn等=1/2kN。这里kp和kn分别为与非门的伏在关和输入管的k值。图2-4(c)表示出单门开关时的电流流通途径和等效倒相器。这时在转换区中,电流流经过一只T1管和串联的T3和T4管。因为A端接固定的高电平,使T2管永远保持截止。等效倒相器分别有kp等=kp和kn等=1/2kn。由以上分析可以看出,当单门开关和双门开关时,在转换区内,这个与非门两种不同的状态,可以用两个不同性质的倒相器来等效。所以呈现出不同的传输特性。

2、CMOS与非门芯片解剖:

在本章我们将以MC14011B芯片为例进行解剖,找出这个与非门。

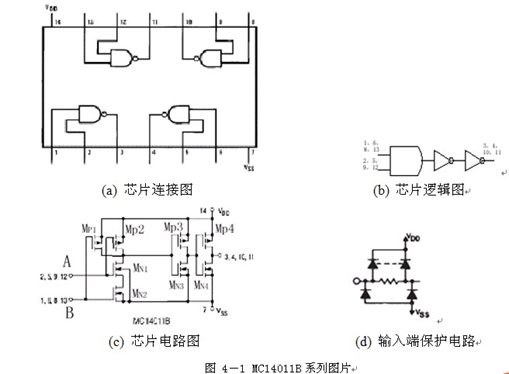

CD4011是一个四个两输入的与非门电路,他遵从标准的B系列输出驱动。该器件也包括了输出缓冲来提供高的增益以次提高传输特性。所有的输入端口都有二极管保护防止静态电流直接从VDD传输到VSS。

下图为a为CD4011的芯片连接图,b是它的逻辑电路,c是芯片内部的一个单元的电路图,d是输入栅保护电路:(从摩托罗拉公司网站下载编辑的)

MC14011B芯片解剖过程:

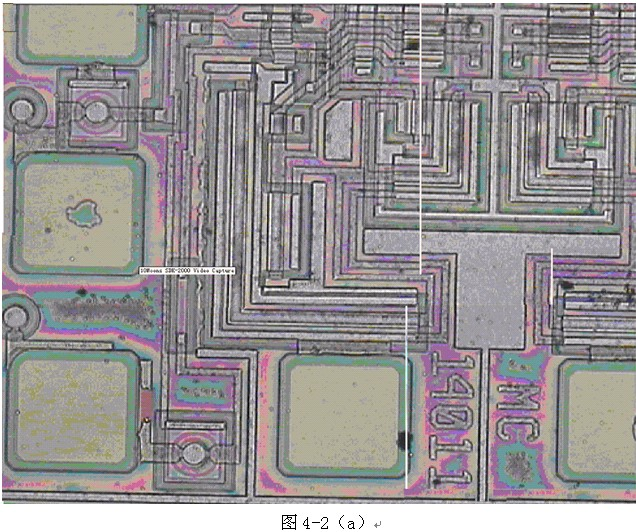

(1)拼图。由于本课题采用的是Motorola的CD4011芯片,其腐蚀难度比较大,所以备用两种照片,一种为有Al线的照片(已经除去氧化层),表面黑白分明,由于Al反光形成白色,所以看不到具体的管子;另一种为无Al线的照片,可以看到有源区、栅、扩散电阻等。

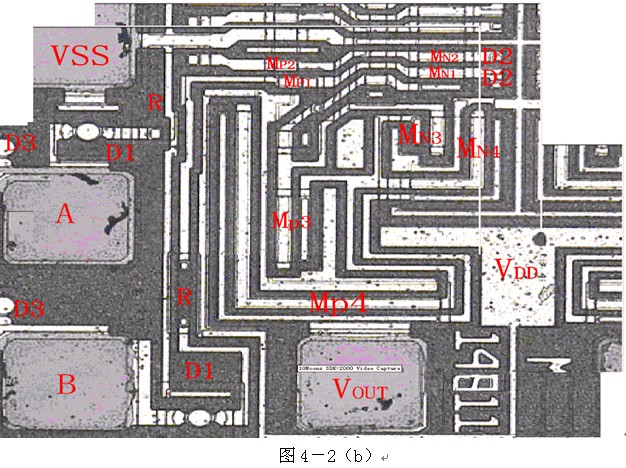

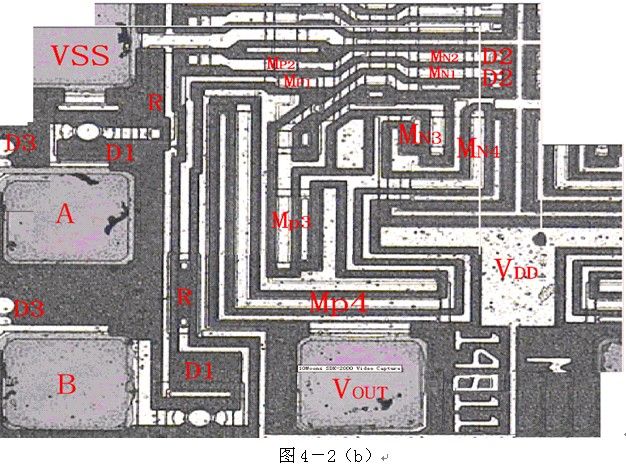

开始拼接前,在实验室用金相显微镜将芯片一个单元按一定的次序依次拍照,最后再拍一张全局图,图像虽不清晰,但可以作为后来拼图的依据。然后按顺序将图片排好,寻找相邻照片的共同点,用图像处理程序将其拼接起来。注意,由于照片可能有些偏差,不可能完全对上,因此只要重合最重要的部分,而且对准的时候从中心开始,这样可以保证中间的重叠比较好,外部可适当放低要求。本试验所拼版图照片如图4-2(a)、(b)

(2)标注。由2-3节提供的芯片管角图和电路图,寻找对应的电源Vdd和GND(Vss)的压焊块,找到后,确定输入输出压焊块,并注明功能,标号,如图4-2(b)。

(3)分块。从压焊块出发,经输入输出电路向内部走线,找到各输入端在内部的入口及各输出端在内部的出口,并做标记。由此将版图分成若干功能块,由输入信号确定各功能块的功能。

(4) 将各个功能块连在一起,画出总体逻辑图,提取各输出端逻辑表达式,进行时序逻辑分析。

(5)提取设计规则,量取各个管的宽长比标于电路图上,分析电路的特点。

(6)分析版图上的防止闭锁效应的措施。

(7)提取版图的布局布线,分析布局布线的整体特点。

(8)研究P阱和衬底接电位的问题。

MC14011B芯片分析过程:

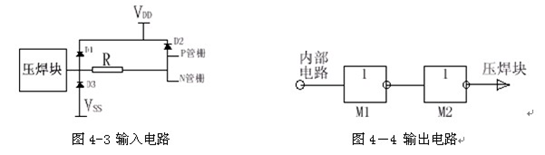

1) 输入电路

该电路的输入电路由压焊块、电阻R、四个二极管组成。如图4-3:

输入信号通过R加入到电路内部。D1、D2、D3分别保护P管和N管的栅不被过大的电流而烧坏,二极管导通电阻r<<R,这样有利于栅上感应电荷的迅速泄放。

其具体的参数见3-5-2节,但与图3-8比较可以发现,这里的D3不是电阻R的寄生二极管,而是专门做出来的,但具体的参数以及相应的击穿电压同3-5-2节。

2) 输出电路

输出电路由两级反向器构成,如图4-4。一般来讲M1相对于M2来说W/L略小,它只驱动M2,起到匹配和整形作用。而M2的W/L很大,可以提供大的负载,为了达到克放电的匹配一般(W/L)P/(W/L)N=2~3。具体见3-5-3节输出电路。

输出电路由于W/L较大,所以往往采用折线和并联的管子的方法以减小面积,从我们的所拍的版图照片中也可以得到验证。

3) 核心电路分析

本芯片的内部主逻辑单元的电路图如图4-1(C)所示,其对应的MOS管在图4-2(b)中已标出,其逻辑功能如下:

当A=0,B=0时,MN1、MN2都截止,MP1、MP2导通,所以输出电平被上拉至VDD,即输出为“1”。

当A=0,B=1时,MN1、Mp1截止,MN2、MP2导通,所以输出也为VDD,即逻辑“1”。

当A=1,B=0时,MN1、Mp1导通,MN2、MP2截止,输出也为VDD,即逻辑“1”。

当A=1,B=1时,MN1、MN2导通,MP1、MP2截止,所以输出为VSS,即逻辑“0”。

综上所述,A、B所实现的功能为,与预期的理论完全吻合,所以从版图上提取的电路是正确的。

MC14011B芯片设计规则(Design rule)

MC14011B芯片采用了标准的Al栅CMOS工艺所做,从实际版图中提取出来的沟道长度我们得知其特征尺寸即L=8um。由于腐蚀的时候将表面的氧化层也腐蚀掉了一部分,所以整个版图看起来有些花,这里仅测量了沟道长度,但基本上还是能与标准的规则一致。

但在测量中,可能某些部分的线宽可能要比实际的要细,可以从几个简单的实例加以说明:

1)孔与孔之间的间距比较小。

打孔本身就是为了形成良好接触,孔的数目较多可以保证电位相等。这里其孔宽度变小,是由于光刻时曝光不充分,加上横向刻蚀引起图形中孔两端呈圆形突出,使孔间距变小,否则孔间距能达到预定值。

2)铝条最小宽度变窄。

A1条要求最小宽度是为保证良好的电导,在实测中比规则小,是因为AI条被刻蚀细了,或解剖时被腐蚀细了。

A1条变细对电路来说是不利的,尤其是大电流时存在电迁移现象,而且在实际中如果刻Al工艺不过关,就很易发生A1条断路,造成电路功能失效。

3) 为了防止Latch-up效应,也同时为了Al线布线的方便,有源区间距拉大,最小间距也加大。

4)在实际中A1条对引线孔必须有一定的覆盖量,规则规定用1λ为标准。如果不要求覆盖1λ,当发生套刻误差时,会发生孔有一部分在Al条外部。有一部分PN结裸露在外面,没有被Al覆盖形成保护,而周围气氛中难免会有杂质,脏物沾污裸露的PN结,使PN结特性变坏,往往也会造成器件总体失效。

总体上看MC14011B电路的布局是很有规律的,周围环绕压焊块,中间放置四个与非门,输入输出附近各自有自己的输入保护电路和输出缓冲单元。中间是走线通道;各压焊块间隔均匀,对称分布于四周;电源和地的压焊块位于两端。

而且该芯片的布线也极有规律。布线在通道中通过,基本走直线或直角线。其中主通道通过打到衬底的通孔横贯上下,各模块之间的联系也有通道完成。

此电路的电源布线总体看走的是大环形,包住各部分,并且VDD和VSS走线平行。在外围电路中,压焊块将VDD和VSS分开,并行与压焊块联便。在内部电路中,VDD和VSS经各自的通道送入内部单元,二者没有发生交叉现象。在内部单元与压焊块之间,VSS追款,它要给两边供电,因此电流较大,需要加宽Al线。

以上为逆向设计的思路,不放给入门的人一点参考吧。但是谨记 不要抄袭,要原创!

支付宝打赏

支付宝打赏  微信打赏

微信打赏