P-Si与N-Si的美丽邂逅–PN结 (转)

本文转自芯苑,ic-garden.cn (由于芯苑会经常关闭站点,故转载存留)

学习半导体器件,必须读懂PN结(PN junction),它是所有器件理论的基础,所以的器件都是靠PN结组成的,不学PN结,讲device就是空中楼阁。

我们知道硅(台湾叫“矽”, Si)是半导体,导电性介于导体和绝缘体之间。不是说它的节电(dielectric)常熟介于之间哦,而是说纯硅(pure Si)的时候不导电,但是掺入一定杂质后就导电了。由这种半导体做出来的器件就叫做半导体器件。简单吧!

下面讨论下掺杂怎么让它导电的,我们知道Si在元素周期表里为四价,所以当他掺入三价的B/Ga/In,因为他们最外层只有三个电子,如果要与Si形成8个电子稳定的共价键则需要从外界吸收一个电子,所以外面多了空穴而带正电,所以我们称掺了三价原子的Si为P型硅(P-Si),而被掺杂原子因为要接受一个电子,称之为受主(Acceptor)。如果往硅里面掺入五价的P/As/Sb元素的时候,因为最外层有5个电子,与硅形成稳定的8个电子共价键的时候,还剩一个多余的电子带负电,所以我们称之为N-Si,而被掺杂的原子因为要给出一个电子,所以称之为施主(Donor)。记住一个概念,虽然P-Si和N-Si为带空穴或电子,但是这两种半导体本身是不带电的。(如果搞不清楚的可以私下问我,别到时候面试被问到不知道就丢人了。),它只是改变了导电特性,本身不带电。另外一个概念对理解器件很重要,不管是P-Si还是N-Si不是只单一含有空穴或电子,而是两者都有。只是P-Si的空穴为多数载流子(Majority),而电子为少数载流子(Minority),反之N-Si的电子为多数载流子,而空穴为少数载流子。

下面讨论,当P-Si与N-Si碰到一块会怎么样?干柴碰烈火了!我们知道当浓度差一定会发生扩散,所以P-Si的多子(majority)空穴会穿过界面流入N-Si一侧与电子复合,而N-Si的多子电子也会穿过界面流入P-Si一侧与空穴复合。所以在界面两侧会产生空间电荷区,在N-Si一侧如果过来的空穴过多超过复合量,则会堆积少量空穴,而在P-Si侧也会同理堆积少量电子。这样在P-Si和N-Si的两侧也会产生一个反向的电压差产生内建电场抑制浓度差造成的扩散(书上称之为漂移),最终达到扩散和漂移相等的动态平衡。(如下图,能带图部分本篇末尾再介绍,有兴趣再阅读)

下面讨论下PN结/二极管(PN结也叫二极管)的导电特性。

1. 当P-Si加正电压/N-Si加负电压时,我们称之为正偏(Forward Bias)。此时势垒降低,我们刚刚讲的动态平衡就会被打破,此时相当于P-Si给了更多的空穴用于抵消P-Si那边的N型空间电荷去,N-Si给了更多的电子用于消耗N-Si那边的P型空间电荷去,所以空间电荷去宽度变小,正向电流电流增大。当两个空间电荷去消失则直接变为导体就饱和了。

2. 当P-Si加负电压/N-Si加正电压时,称之为反偏(Reverse Bias)。此时势垒增高,按照刚刚的理论则空间电荷区会变宽,但是不会无限变宽直之截至。因为反向电压增强到某个临界值,则电场增强会导致电子碰撞产生新的电子空穴对(Electro-hole Pair),而产生的电子继续在电场下碰撞继续产生,如此滚雪球碰撞就产生了雪崩击穿(Avalanche Breakdown, BV).

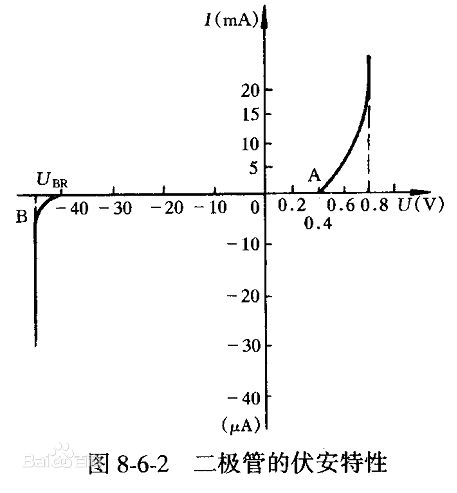

所以简化PN结和二极管的电压/电流(I-V)特性曲线如下(正向导通反向截止):在正向电压下先空间电荷区逐渐减小,电流逐渐增大,最后直接导通。在反向电压下,空间电荷去增宽,所以一直截止,直至击穿。正向导通电压只要是Si几乎都是0.6~0.8V,由它的尽带宽度(Forbbiden Area)决定的。如果是Ge几乎是0.4~0.6V。但是反向击穿电压则随着两边浓度变化而变化,总体是浓度增加击穿电压减小。(原因你猜猜看,如果想不通可以来找我~~)

如果单纯用二极管作为器件,主要利用它的正向导通反向截止:

1. 整流:交流变直流,因为交流相位发生变化,所以正向导通反向截止是的单向位通过则实现直流。

2. 钳位 (Clamp)/稳压: 在电路输入端旁路并联一个反向的二极管,正常工作时,因为二极管反向截止,所以可以忽略,但是当电压升高时,则旁路二极管反向击穿短路则保护了电路被烧毁。这也是早起比较简单的ESD保护电路,只是我们要通过调整dopping来实现反向击穿电压值。

3. 变容:我们没有讲一个概念,空间电荷区,其实是一个电容重放电的过程,所以这个空间电荷区也是一个电容,通过改变这个宽度实现电容的调整,这个比较多应用在简单的震荡器和频率调制等。

大概就讲这些吧,以后讲到HV器件的Breakdown再给大家讲突变结(Abrupt)和缓变结(Gradiant)。

这里再附带讲一下文中的能带图:

高中化学里面讲原子结构都有个最外层电子的轨道杂化,叫什么基态和激发态等等,我也忘了。但是只要记住基态都是能量比较稳定的,不参与导电的那一部分,而激发态就是比较活跃的那一部分,形象的这样加深记忆就好了。在半导体里面就各自分为导带(Conduction band)和价带(valance band),顾名思义就是能够导电的电子层所在区域和不能导电的区域。

从不导电的价带到导电中间的区域为禁带(Forbidden Band),必须要有足够的能量,才能跃迁过这个区域达到导带参与导电,而这个跃迁所需的能量就是禁带宽度(eV),尽带宽度就是物理上定义为导体和绝缘体的指标。(绝缘体的禁带宽度~4.5eV,而半导体0.1~2eV)

禁带宽度里面还有个词叫做费米能级,这个东西要从量子力学说起,话说这个粒子都是一直在那里无规则热震动的(万物都是运动的),所以它会在某个位置或相邻位置来回运动,每个电子都有自己的位置(量子态),但每个位置同时只有一个粒子/电子,遵循鲍利不相容原理。。。。。不说了。太复杂了。直接给你个简单的方法记住费米能级位置(多数载流子位置),因为P型半导体多子为空穴,所以很少电子,所以导带很少电子,所以费米能级靠近价带。而N型半导体多子为电子,自然占据了导带,所以费米能级靠近导带。

能带图在解释后面的导电特性很有用,当然你也可以用其他方法解释,只要行得通,只是最权威最foundmental的解释就是能带。

支付宝打赏

支付宝打赏  微信打赏

微信打赏